# LT7589

## High Performance Uart TFT Display Controller

## **Specification**

V1.3

www.levetop.cn

Levetop Semiconductor Co., Ltd.

## **Version History**

| Version | Release Date | Description                                                                                                                                                       |

|---------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0    | 2024/11/22   | LT7589 Preliminary Release                                                                                                                                        |

| V1.1    | 2025/03/20   | <ul> <li>Update Pin - VDD33_IO Description</li> <li>Update Application Circuit</li> </ul>                                                                         |

| V1.2    | 2025/04/21   | <ul> <li>Modify the pin signal description of "LCD_XI"</li> <li>Update Table 6-4 External Flash Signal Description</li> <li>Update Application Circuit</li> </ul> |

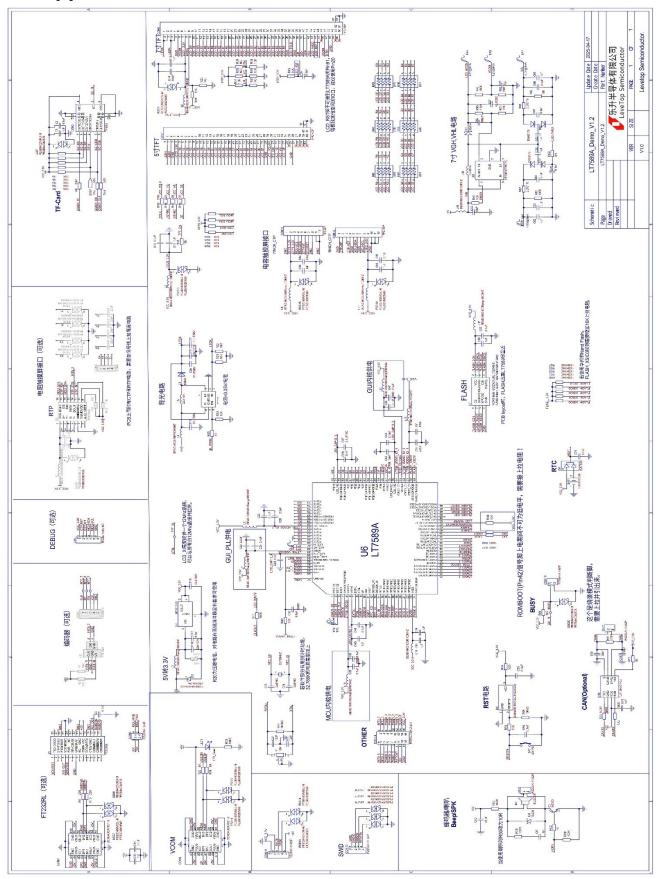

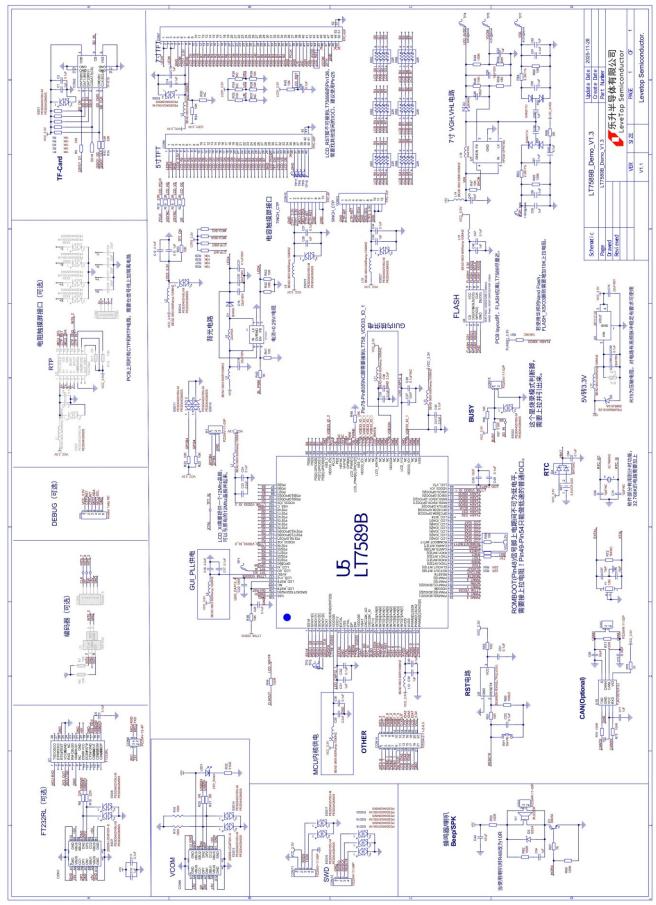

| V1.3    | 2025/11/28   | <ul><li>Table 28-1: QFN-96Pin Dimensions</li><li>Figure 29-2: LT7589B Application Circuit</li></ul>                                                               |

## Copyright

The copyright of this document belongs to Levetop Semiconductor Co., Ltd. If you need to copy or duplicate it, please obtain Levetop Semiconductor's permission in advance. Although the information recorded in this document has been proofread, Levetop Semiconductor assumes no responsibility for the specifications of the document usage instructions. The applications mentioned in the document are for reference only, and Levetop Semiconductor does not guarantee that such applications do not require further modification. Levetop Semiconductor reserves the right to change its product specifications or documents without prior notice. For the latest product information, please visit our website Https://www.levetop.cn.

## **Content**

| Copyright       2         Content       3         Figure List       .12         Table List       .19         1. Chip Introduction       .22         1.1. Basic Introduction       .22         1.2. Application Block Diagram       .24         1.3. Internal Block Diagram       .24         1.4. Features       .25         2. Pin Description       .27         2.1. Pin Assignment       .27         2.2. Pin Description       .29         2.2.1. SCI (Uarl) Signals       .29         2.2.2. LCD Panel Signals       .30         2.2.3. QSPI Signals       .31         2.2.4. External Flash Signals       .32         2.2.5. PWM Signals       .33         2.2.6. USB Signals       .35         2.2.7. GPIO and Interrupt Signals       .35         2.2.8. ADC Input Signals       .35         2.2.9. Miscellaneous Signals       .37         2.2.10. Power and Clock Signals       .37         2.2.10. Power and Clock Signals       .36         3.3. GPIO Resources of Different TFT Panels       .41         3.1. Serial Uart Interface       .43         3.2. Serial TFT Panel Protocol Table       .45         3.3. Program Code Devel                                                  | Ve | ersion History                            | 2  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------|----|

| Figure List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Co | ppyright                                  | 2  |

| Figure List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Co | ontent                                    | 3  |

| Table List       .19         1. Chip Introduction       .22         1.1. Basic Introduction       .22         1.2. Application Block Diagram       .22         1.3. Internal Block Diagram       .24         1.4. Features       .25         2. Pin Description       .27         2.1. Pin Assignment       .27         2.2. Pin Description       .29         2.2.1. SCI (Uart) Signals       .29         2.2.2. LCD Panel Signals       .30         2.2.3. QSPI Signals       .31         2.2.4. External Flash Signals       .32         2.2.5. PVM Signals       .31         2.2.6. USB Signals       .33         2.2.6. USB Signals       .35         2.2.7. GPIO and Interrupt Signals       .35         2.2.8. ADC Input Signals       .37         2.2.9. Miscellaneous Signals       .37         2.2.10. Power and Clock Signals       .38         2.3. GPIO Resources of Different TFT Panels       .41         3. Function Description       .43         3.1. Serial Uart Interface       .43         3.2. Serial TFT Panel Protocol Table       .45         3.3. Program Code Develop.       .45         3.4.1. Interface of TFT LCD Panel       .46 </td <td></td> <td></td> <td></td> |    |                                           |    |

| 1. Chip Introduction       .22         1.1. Basic Introduction       .22         1.2. Application Block Diagram       .22         1.3. Internal Block Diagram       .24         1.4. Features       .25         2. Pin Description       .27         2.1. Pin Assignment       .27         2.2. Pin Description       .29         2.2.1. SCI (Uart) Signals       .29         2.2.2. LCD Panel Signals       .30         2.2.3. QSPI Signals       .31         2.2.4. External Flash Signals       .32         2.2.5. PWM Signals       .33         2.2.6. USB Signals       .33         2.2.7. GPIO and Interrupt Signals       .35         2.2.8. ADC Input Signals       .35         2.2.9. Miscellaneous Signals       .37         2.2.9. Miscellaneous Signals       .37         2.2.10. Power and Clock Signals       .38         2.3. GPIO Resources of Different TFT Panels       .41         3. Function Description       .43         3.1. Serial Uart Interface       .43         3.2. Serial TFT Panel Protocol Table       .45         3.3. Program Code Develop       .45         3.4.1. Interface of TFT LCD Panel       .46         3.4.2. SSI (Synchronous Serial I               | •  |                                           |    |

| 1.1. Basic Introduction       22         1.2. Application Block Diagram       22         1.3. Internal Block Diagram       24         1.4. Features       25         2. Pin Description       27         2.1. Pin Assignment       27         2.2. Pin Description       29         2.2.1. SCI (Uart) Signals       29         2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       35         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4.               |    |                                           |    |

| 1.2. Application Block Diagram       22         1.3. Internal Block Diagram       24         1.4. Features       25         2. Pin Description       27         2.1. Pin Assignment       27         2.2. Pin Description       29         2.2.1. SCI (Uart) Signals       29         2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       35         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48          3.4.4. ADC A                       | 1. | Cnip introduction                         | 22 |

| 1.3. Internal Block Diagram       24         1.4. Features       25         2. Pin Description       27         2.1. Pin Assignment       27         2.2. Pin Description       29         2.2.1. SCI (Uart) Signals       29         2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                   |    | 1.1. Basic Introduction                   | 22 |

| 1.4. Features       25         2. Pin Description       27         2.1. Pin Assignment       27         2.2. Pin Description       29         2.2.1. SCI (Uart) Signals       29         2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                |    | 1.2. Application Block Diagram            | 22 |

| 2. Pin Description       27         2.1. Pin Assignment       27         2.2. Pin Description       29         2.2.1. SCI (Uart) Signals       29         2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                               |    | 1.3. Internal Block Diagram               | 24 |

| 2.1. Pin Assignment       27         2.2. Pin Description       29         2.2.1. SCI (Uart) Signals       29         2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                   |    | 1.4. Features                             | 25 |

| 2.1. Pin Assignment       27         2.2. Pin Description       29         2.2.1. SCI (Uart) Signals       29         2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                   | 2. | Pin Description                           | 27 |

| 2.2. Pin Description       29         2.2.1. SCI (Uart) Signals       29         2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                        |    | 2.1. Pin Assignment                       | 27 |

| 2.2.1. SCI (Uart) Signals       29         2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                              |    |                                           |    |

| 2.2.2. LCD Panel Signals       30         2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                         |    |                                           |    |

| 2.2.3. QSPI Signals       31         2.2.4. External Flash Signals       32         2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                             |    |                                           |    |

| 2.2.5. PWM Signals       33         2.2.6. USB Signals       35         2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                                                       |    |                                           |    |

| 2.2.6. USB Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                                           |    |

| 2.2.7. GPIO and Interrupt Signals       35         2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                                           |    |

| 2.2.8. ADC Input Signals       37         2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |                                           |    |

| 2.2.9. Miscellaneous Signals       37         2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 3                                         |    |

| 2.2.10. Power and Clock Signals       38         2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       .43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                                           |    |

| 2.3. GPIO Resources of Different TFT Panels       41         3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                                           |    |

| 3. Function Description       43         3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                                           |    |

| 3.1. Serial Uart Interface       43         3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _  |                                           |    |

| 3.2. Serial TFT Panel Protocol Table       45         3.3. Program Code Develop       45         3.4. The Application of Chip's Interface       46         3.4.1. Interface of TFT LCD Panel       46         3.4.2. SSI (Synchronous Serial Interface)       47         3.4.3. SCI (Serial Communication Interface)       48         3.4.4. ADC Analog Input       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3. | Function Description                      | 43 |

| 3.3. Program Code Develop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 3.1. Serial Uart Interface                | 43 |

| 3.4. The Application of Chip's Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 3.2. Serial TFT Panel Protocol Table      | 45 |

| 3.4.1. Interface of TFT LCD Panel463.4.2. SSI (Synchronous Serial Interface)473.4.3. SCI (Serial Communication Interface)483.4.4. ADC Analog Input48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 3.3. Program Code Develop                 | 45 |

| 3.4.2. SSI (Synchronous Serial Interface)473.4.3. SCI (Serial Communication Interface)483.4.4. ADC Analog Input48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 3.4. The Application of Chip's Interface  | 46 |

| 3.4.3. SCI (Serial Communication Interface) 48 3.4.4. ADC Analog Input 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 3.4.1. Interface of TFT LCD Panel         | 46 |

| 3.4.4. ADC Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 3.4.2. SSI (Synchronous Serial Interface) | 47 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | · ·                                       |    |

| 3.4.5. GPIO and Interrupt Signals49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 3.4.5. GPIO and Interrupt Signals         | 49 |

|    | 3.4.6. PWM Output Signals                     |      |

|----|-----------------------------------------------|------|

|    | 3.4.7. USB Interface                          |      |

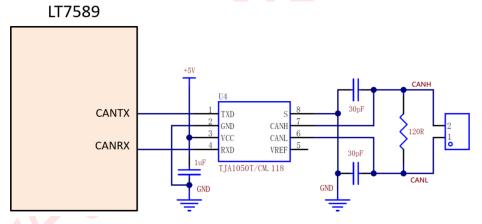

|    | 3.4.8. Canbus Interface                       |      |

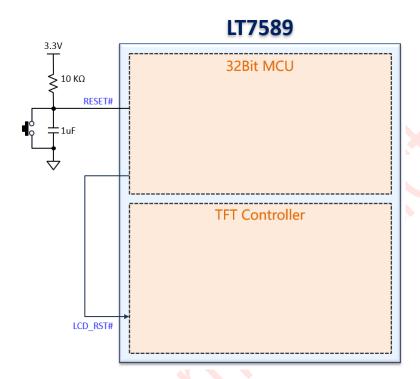

|    | 3.4.10. Reset Signals                         |      |

| 4. |                                               |      |

| т. | 4.1. Features                                 |      |

|    | 4.2. Microarchitecture Summary                |      |

|    | 4.3. Programming Model                        |      |

|    | 4.4. Data Format Summary                      |      |

|    | 4.5. Operand Addressing Capabilities          | 60   |

|    | 4.6. Instruction Set Overview                 | .60  |

| 5. |                                               |      |

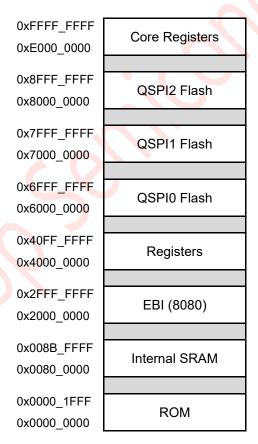

|    | 5.1. Introduction                             | .63  |

|    | 5.2. Address Map                              |      |

| 6. |                                               | 65   |

|    | 6.1. Introduction                             | .65  |

|    | 6.2. Features                                 | .65  |

|    | 6.3. Memory Map and Registers                 | .65  |

|    | 6.3.1. Memory Map                             |      |

|    | 6.3.2. Register Descriptions                  | .66  |

| 7. | Embedded Interrupt Controller(EIC)            | 74   |

|    |                                               | .74  |

|    | 7.2. Features                                 | .74  |

|    | 7.3. Memory Map and Registers                 |      |

|    | 7.3.1. Memory Map                             |      |

|    | 7.4. Function Description                     |      |

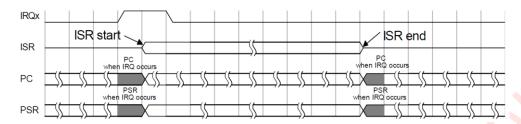

|    | 7.4.1. Interrupt Handling Without Confliction |      |

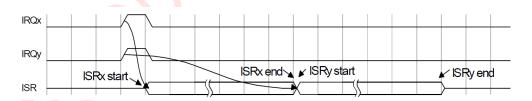

|    | 7.4.2. Interrupt With Confliction             |      |

|    | 7.4.3. Pend Trap Function                     | . 85 |

|    | 7.5. Interrupts                               | .86  |

| 8. | Embedded Programmable Timer (EPT)             | 91   |

|    | 8.1. Introduction                             | .91  |

|    | 8.2. Memory Map and Registers                 | .91  |

|    | LT7589_DS_EN / V1.3                           |      |

|    | 8.2.1. Memory Map                          |     |

|----|--------------------------------------------|-----|

|    | 8.3. Function Description                  |     |

|    | 8.3.1. Count Timing                        |     |

| 9. | Clock and Power Control Module (CLKPWRM)   | 96  |

|    | 9.1. Overview                              | 96  |

|    | 9.2. Features                              | 96  |

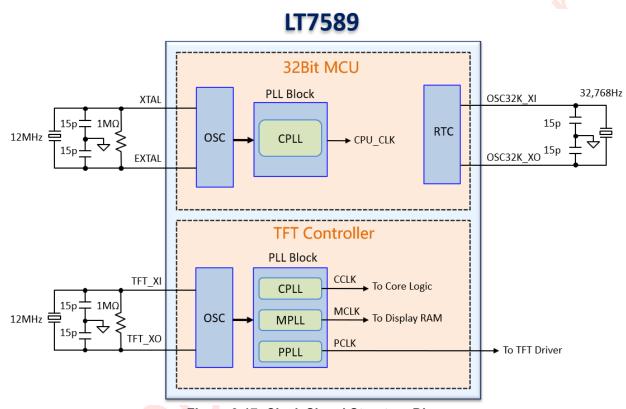

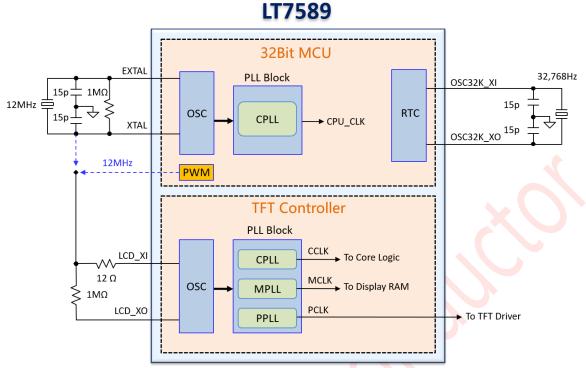

|    | 9.3. Clock Structure                       | 96  |

|    | 9.4. Clock Source Select                   | 97  |

|    | 9.4.1. Low-Power Options                   | 97  |

|    | 9.5. Memory Map and Registers              | 97  |

|    | 9.5.1. Memory Map                          |     |

|    | 9.5.2. Register Description                |     |

|    | 9.6. Functional Description                | 115 |

|    | 9.6.2. The Frequency of PLL Measurement    |     |

|    | 9.6.3. The Frequency of 128KHz Measurement | 115 |

| 10 | Reset Control Module (RCM)                 | 116 |

|    | 10.1. Overview                             |     |

|    | 10.2. Features                             | 116 |

|    | 10.3. Block Diagram                        | 116 |

|    | 10.4. Memory Map and Registers             | 117 |

|    | 10.4.1. Memory Map                         |     |

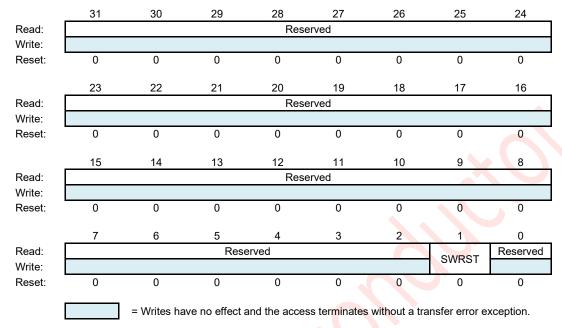

|    | 10.4.2. Register Description               |     |

|    | 10.5. Functional Description               |     |

|    | 10.5.1. Reset Sources                      |     |

| 11 | . Static Random Access Memory (SRAM)       |     |

|    | 11.1. Introduction                         |     |

|    | 11.2. Modes Of Operation                   |     |

|    | 11.3. Low-Power Modes                      |     |

|    | 11.4. Reset Operation                      |     |

|    | 11.5. Interrupts                           |     |

| 12 | Cache Module (CACHEM)                      |     |

|    | 12.1. Introduction                         |     |

|    |                                            |     |

| 12.2. Block Diagram                                                                              | 124 |

|--------------------------------------------------------------------------------------------------|-----|

| 12.3. Memory Map and Registers                                                                   | 125 |

| 12.4. Cache Function                                                                             | 135 |

| 12.5. Cache Control                                                                              | 136 |

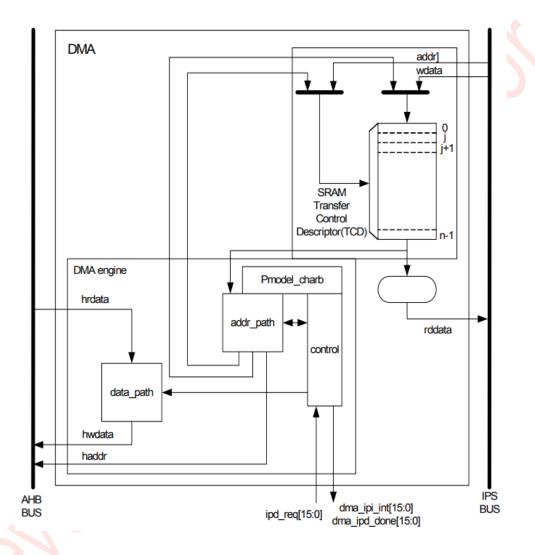

| 13. Direct Memory Access Controller (DMAC)                                                       | 140 |

| 13.1. Information Specific of DMA Controller  13.1.1. DMAC Features  13.1.2. Channel Assignments | 140 |

| 13.2. Introduction                                                                               |     |

| 13.2.1. Features                                                                                 |     |

| 14.1. Memory Map and Registers                                                                   | 144 |

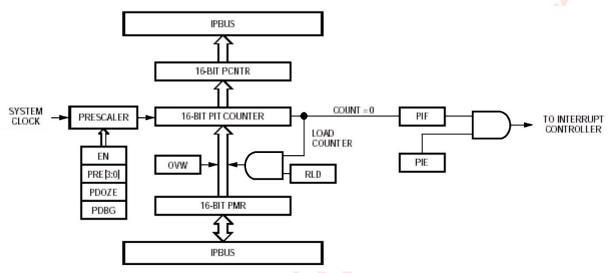

| 15. Programmable Interrupt Timer (PIT)                                                           |     |

| 15.1. Introduction                                                                               |     |

| 15.2. Block Diagram                                                                              | 157 |

| 15.3. Modes of Operation                                                                         |     |

| 15.4. Signals                                                                                    | 158 |

| 15.5. Memory Map and Registers  15.5.1. Memory Map                                               | 158 |

| 15.6. Functional Descripiton                                                                     | 162 |

| 15.7. Interrupt Operation                                                                        | 163 |

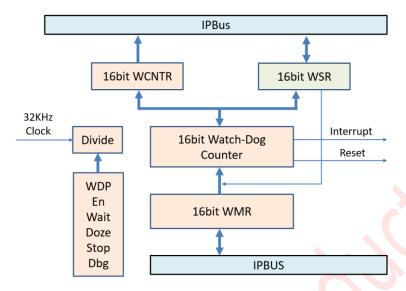

| 16. Watchdog Timer (WDT)                                                                         | 164 |

| 16.1. Introduction                                                                               | 164 |

| LT7589_DS_EN / V1.3                                                                              |     |

|    | 16.2. Modes of Operation                             | 164   |

|----|------------------------------------------------------|-------|

|    | 16.2.1. Wait Mode                                    | .164  |

|    | 16.2.2. Doze Mode                                    | .164  |

|    | 16.2.3. Stop Mode                                    |       |

|    | 16.2.4. Debug Mode                                   | 164   |

|    | 16.3. Block Diagram                                  | 165   |

|    | 16.4. Signals                                        | 165   |

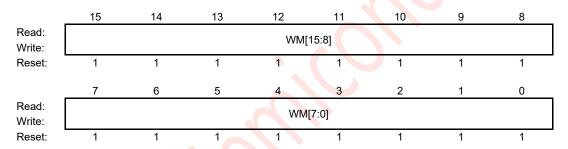

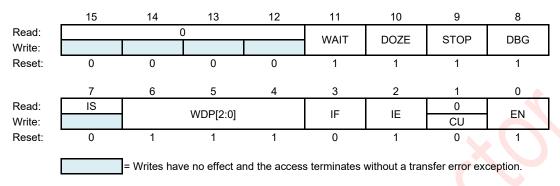

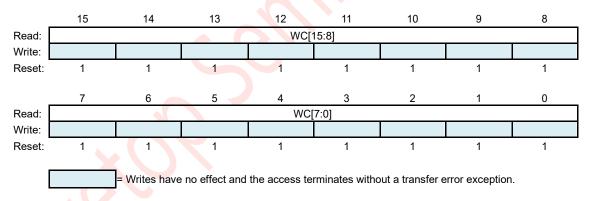

|    | 16.5. Memory Map and Registers                       | 165   |

|    | 16.5.1. Memory Map                                   |       |

|    | 16.5.2. Register Description                         |       |

| 17 | .Real Time Controller (RTC)                          | .170  |

|    | 17.1. Introduction                                   | 170   |

|    | 17.2. Features                                       |       |

|    | 17.3. Test Mode                                      | 170   |

|    | 17.4. Block Diagram                                  | 170   |

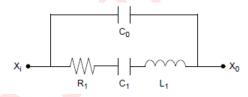

|    | 17.5. Application Circuit                            | 171   |

| 18 | . Edge Port Module (EPORT)                           |       |

|    | 18.1. Introduction                                   | 172   |

|    | 18.2. Low-Power Mode Operation                       | 172   |

|    | 18.2.1. Wait and Doze Modes                          |       |

|    | 18.2.2. Stop Mode                                    | .172  |

|    | 18.3. Interrupt/General-Purpose I/O Pin Descriptions | 173   |

|    | 18.4. Memory Map And Registers                       | 173   |

|    | 18.4.1. Memory Map                                   | . 173 |

|    | 18.4.2. Register Description                         | . 174 |

| 19 | . CANBus Controller(CANBC)                           | .181  |

|    | 19.1. Introduction                                   | 181   |

|    | 19.1.1. Overview                                     | . 181 |

|    | 19.1.2. CANBus Module Features                       | .182  |

|    | 19.1.3. Modes Of Operation                           | . 183 |

|    | 19.2. External Signal Description                    |       |

|    | 19.2.1. Overview                                     |       |

|    | 19.2.2. Signal Descriptions                          | 184   |

| 20 | . Serial Communication Interface (SCI)               | .185  |

|    | 20.1. Introduction                                   | 185   |

|    | 20.2. Features                                       | 185   |

|    |                                                      |       |

LT7589\_DS\_EN / V1.3

|    | 20.3. Modes of                                            | f Operation                                                | 186               |

|----|-----------------------------------------------------------|------------------------------------------------------------|-------------------|

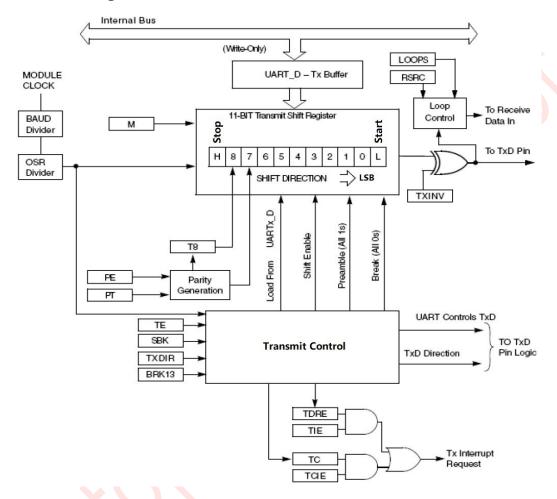

|    | 20.4. Block Dia                                           | agram                                                      | 186               |

|    | 20.5.1. Sto                                               | f Operationp Modeit Mode                                   | 187               |

|    | 20.6. Signal D                                            | escription                                                 | 187               |

|    | 20.7.1. Mer                                               | Map and Registers mory Map gister Description              | 188               |

|    |                                                           | al Description                                             |                   |

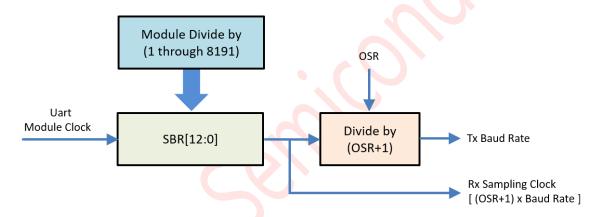

|    |                                                           | te Generation                                              |                   |

|    | 20.10.1.                                                  | ansmitter Functional DescriptionSend Break And Queued Idle | 215               |

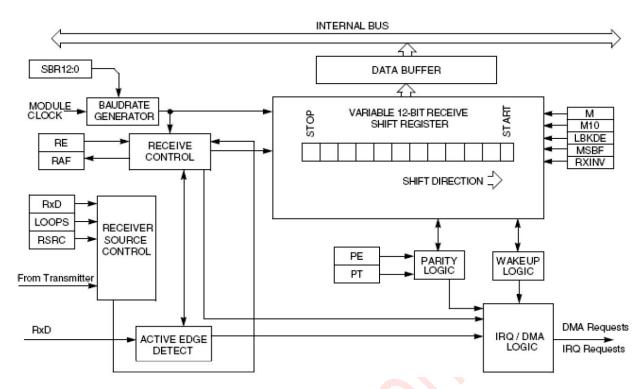

|    | 20.11. Re 20.11.1. 20.11.2. 20.11.3.                      | Data Sampling Technique                                    | 216<br>217        |

|    | 20.12. Ac<br>20.12.1.<br>20.12.2.<br>20.12.3.<br>20.12.4. | Iditional SCI Functions                                    | 221<br>221<br>221 |

|    | 20.13. Inf<br>20.13.1.<br>20.13.2.                        | frared Interface                                           | 222               |

|    | 20.14. Int                                                | terrupts And Status Flags                                  | 223               |

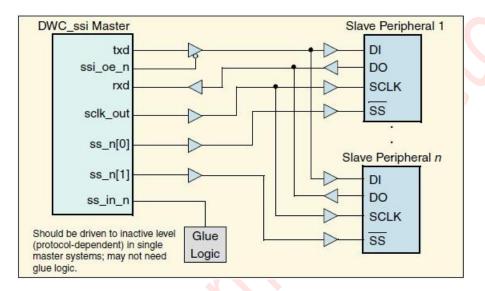

| 21 | . Synchron <mark>o</mark> u                               | s Serial Interface (SSI)                                   | 224               |

|    | 21.1. Introduct                                           | ion                                                        | 224               |

|    | 21.2. Features                                            | )                                                          | 224               |

|    | 21.3. Modes o                                             | f Operation                                                | 224               |

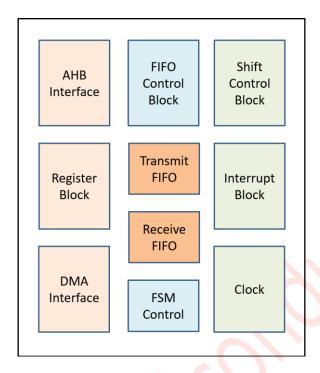

|    | 21.4. Block Dia                                           | agram                                                      | 225               |

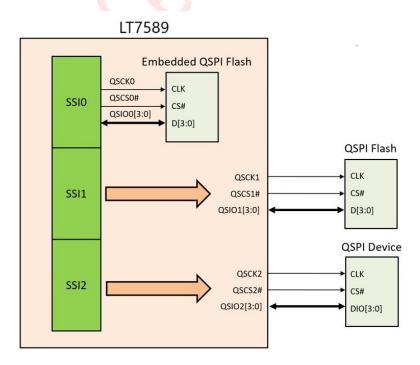

|    | 21.5. Application                                         | on Diagram                                                 | 225               |

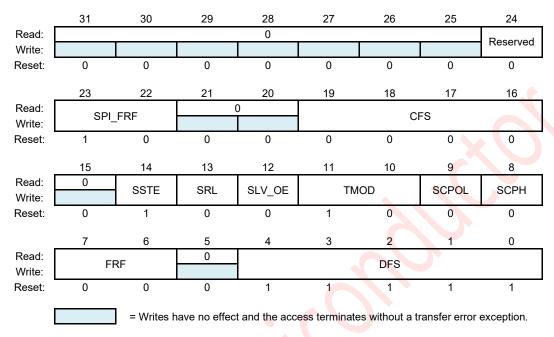

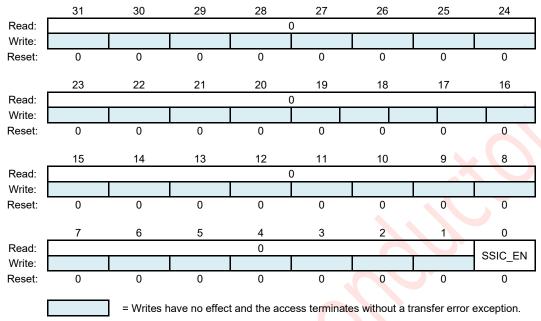

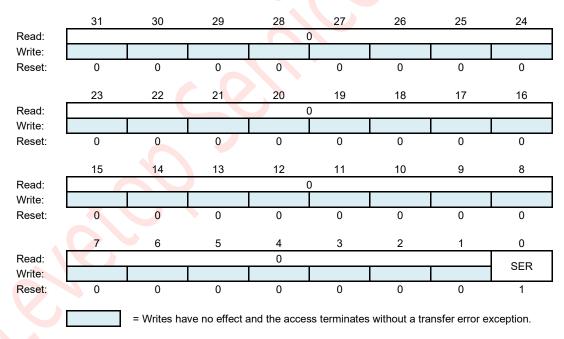

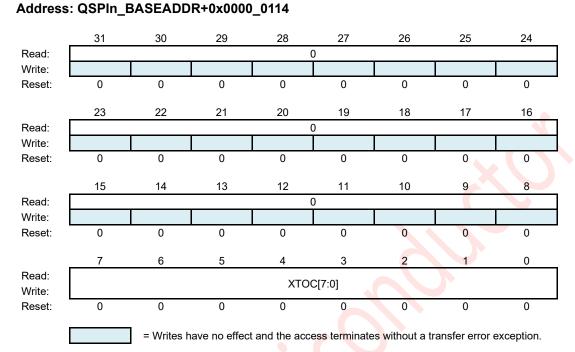

|    | 21.6.1. Mer                                               | Map and Registers<br>mory Mapgister Descriptions           | 226               |

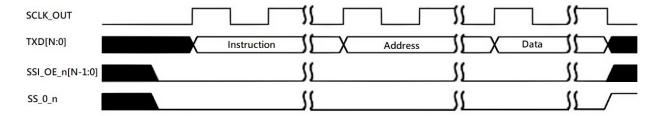

|    |                                                           | al Descriptionster Mode                                    |                   |

|    |                                                           | LT7589_DS_EN / V1.3                                        |                   |

|     | 21.7.2. Clock Ratios                              | 265 |

|-----|---------------------------------------------------|-----|

|     | 21.7.3. Receive and Transmit FIFO Buffers         | 266 |

|     | 21.7.4. DMA Operation                             | 266 |

|     | 21.7.5. SSI Interrupts                            |     |

|     | 21.7.6. Enhanced SPI Modes                        |     |

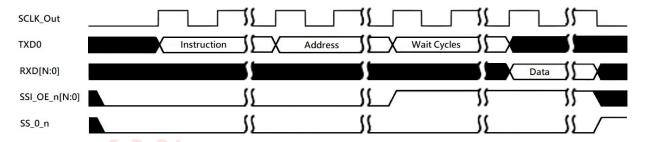

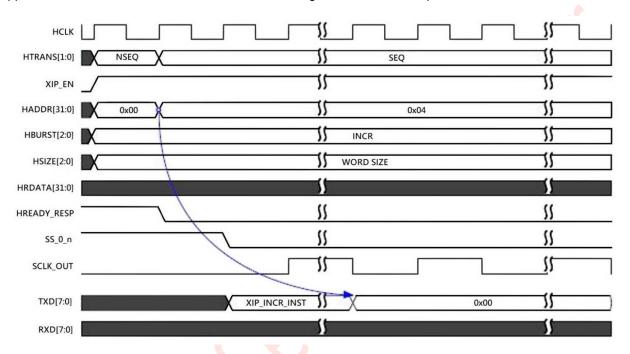

|     | 21.7.7. Execute In Place (XIP) Mode               |     |

|     | 21.7.8. Continuous Transfer Mode in XIP           |     |

|     | 21.7.9. Data Pre-fetch in XIP Operations          | 269 |

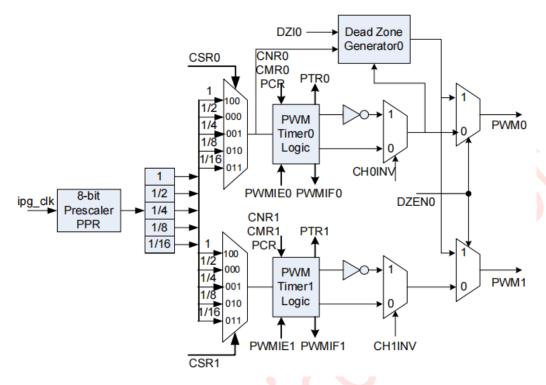

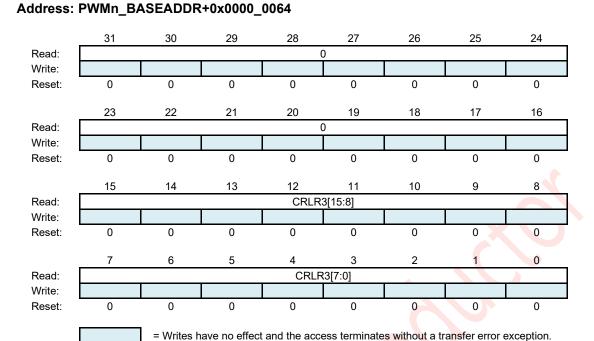

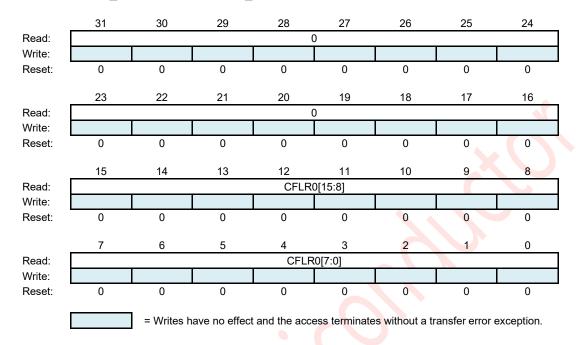

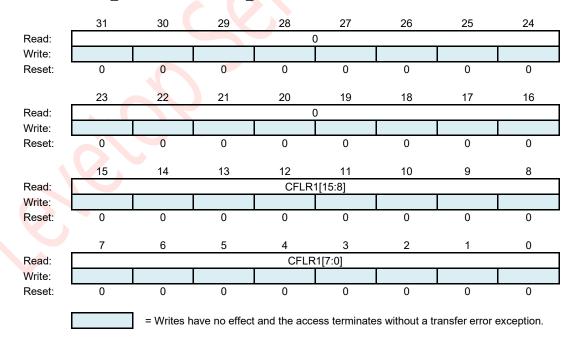

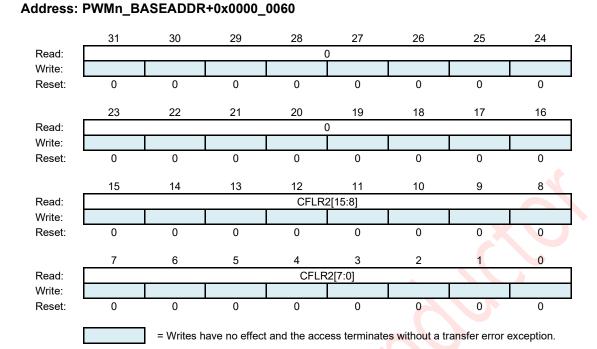

| 22. | .Pulse Width Modulator (PWM)                      | 270 |

|     | 22.1. Introduction                                | 270 |

|     | 22.2. Features                                    | 270 |

|     | 22.3. Block Diagram                               | 271 |

|     | 22.4. Signal Description                          | 271 |

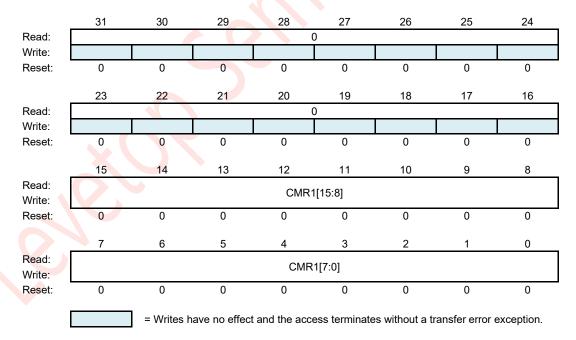

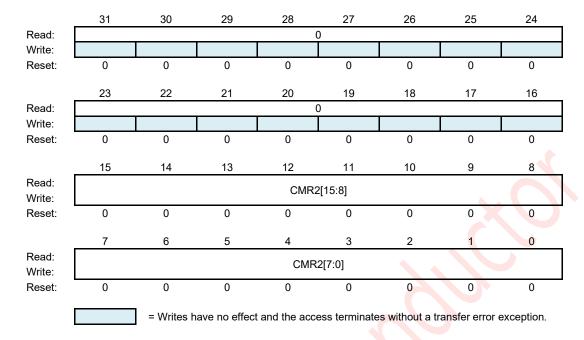

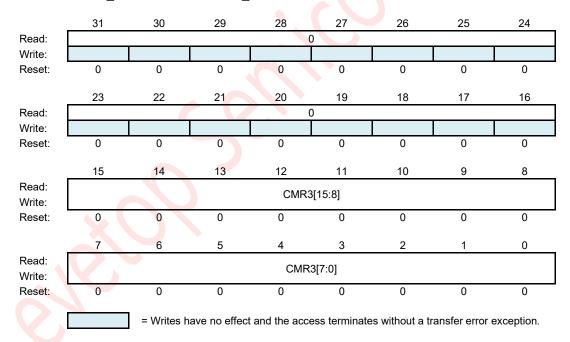

|     | 22.5. Memory Map and Registers                    | 272 |

|     | 22.5.1. Memory Map                                | 272 |

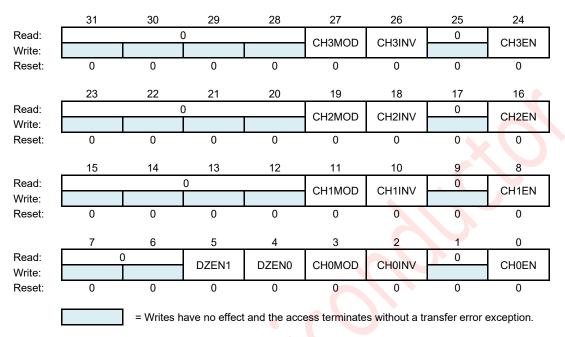

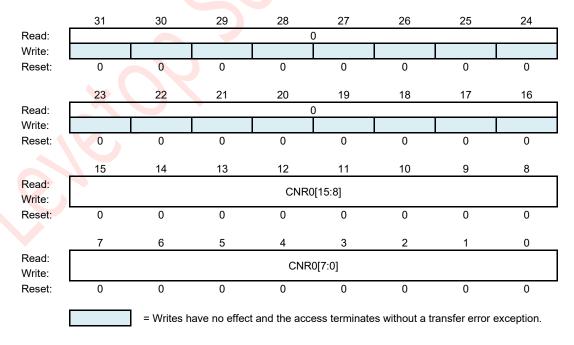

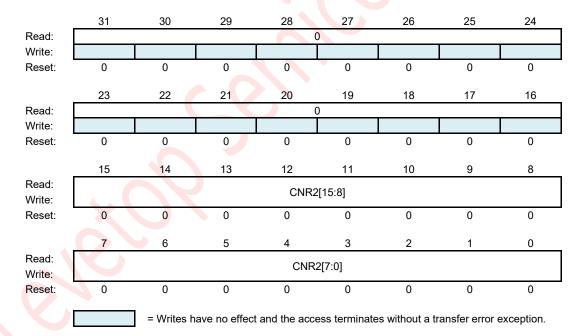

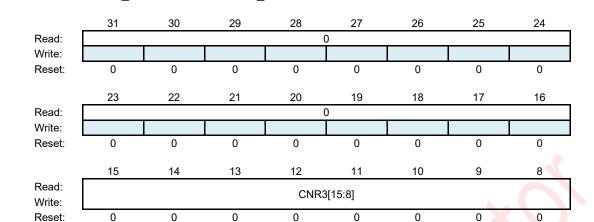

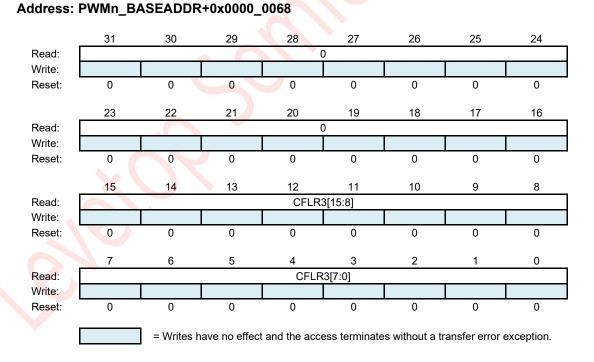

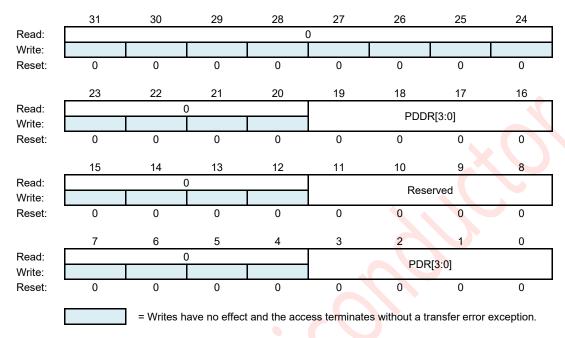

|     | 22.5.2. Register Descriptions                     | 273 |

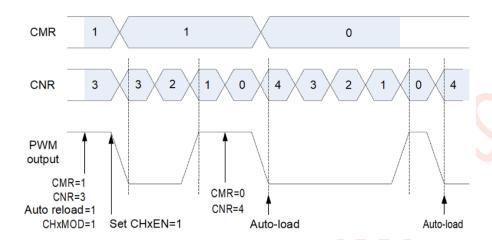

|     | 22.6. Functional Descriptions                     | 295 |

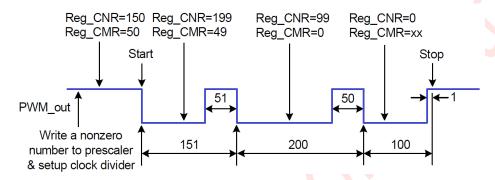

|     | 22.6.1. PWM Double Buffering And Automatic Reload | 295 |

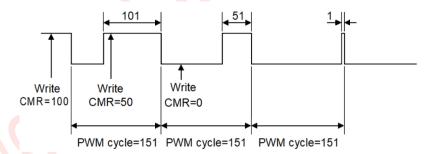

|     | 22.6.2. Modulate Duty Ratio                       |     |

|     | 22.6.3. Dead-Zone Generator                       |     |

|     | 22.6.4. PWM Timer Start Procedure                 |     |

|     | 22.6.5. PWM Timer Stop Procedure                  |     |

|     | 22.6.6. Capture Start Procedure                   |     |

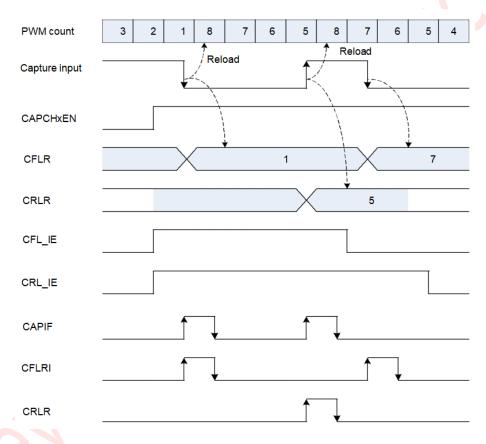

|     | 22.6.7. Capture Basic Timer Operation             | 297 |

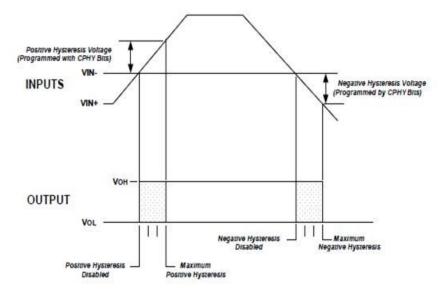

| 23. | . Analog Compar <mark>ator (COM</mark> P)         | 298 |

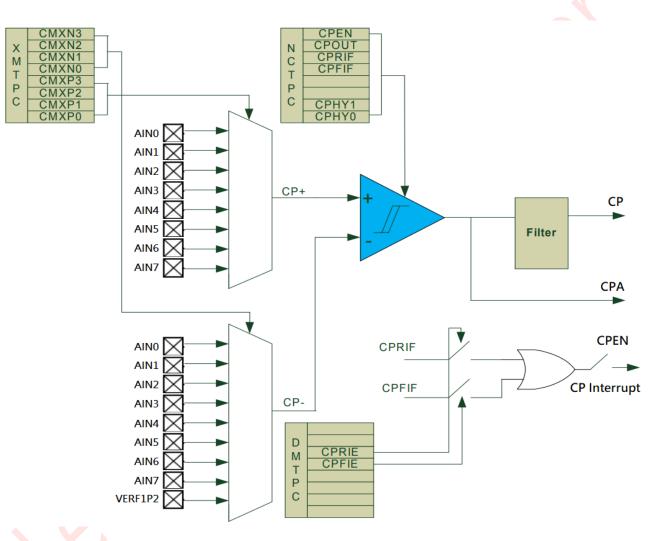

|     | 23.1. Introduction                                | 298 |

|     | 23.2. Block Diagram                               | 298 |

|     | 23.3. Modes of Operation                          | 299 |

|     | 23.3.1. Wait Mode                                 | 299 |

|     | 23.3.2. Doze Mode                                 | 299 |

|     | 23.3.3. Stop Mode                                 | 299 |

|     | 23.4. Memory Map and Registers                    | 299 |

|     | 23.4.1. Memory Map                                | 299 |

|     | 23.4.2. Register Descriptions                     | 300 |

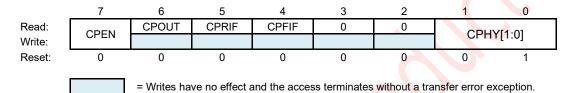

|     | 23.5. Function Description                        | 303 |

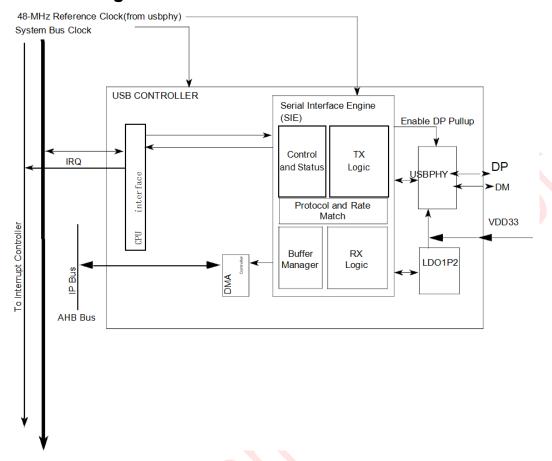

| 24. | . USB2.0 Full-Speed Device Controller (USBC)      | 305 |

|     | 24.1. Introduction                                | 305 |

|    | 24.2. Features                                                      | 305 |

|----|---------------------------------------------------------------------|-----|

|    | 24.3. Block Diagram                                                 | 306 |

|    | 24.4. Modes Of Operation                                            | 306 |

|    | 24.4.1. Wait Mode                                                   | 306 |

|    | 24.4.2. Doze Mode                                                   | 306 |

|    | 24.4.3. Stop Mode                                                   | 306 |

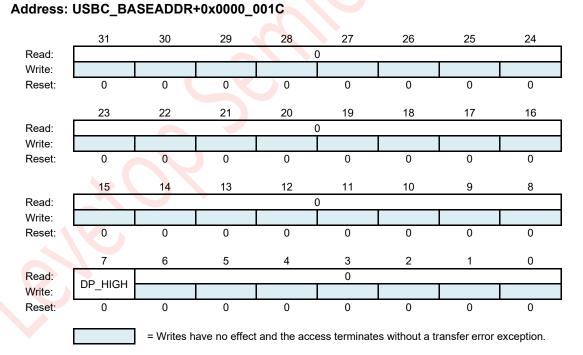

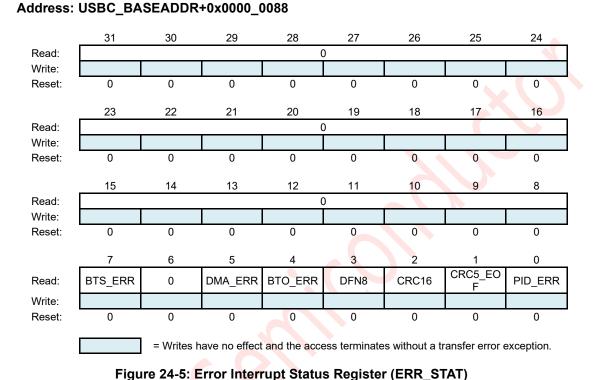

|    | 24.5. Memory Map and Registers                                      | 307 |

|    | 24.5.1. Memory Map                                                  | 307 |

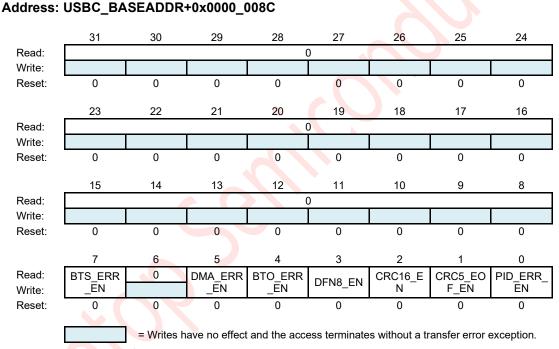

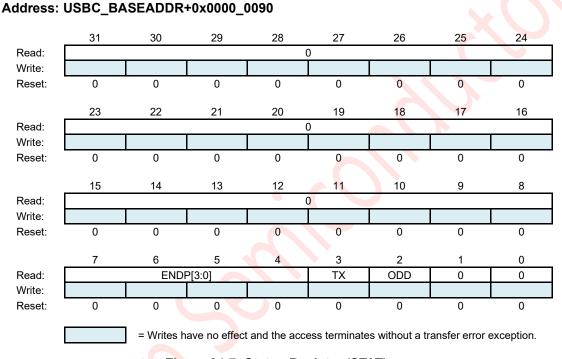

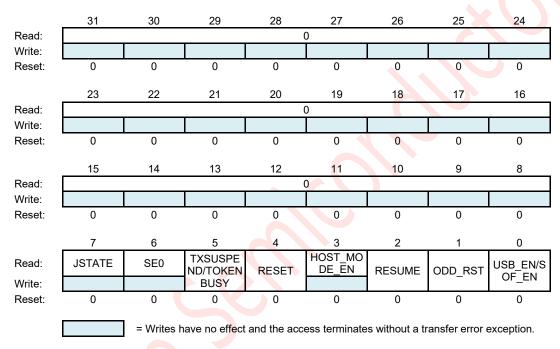

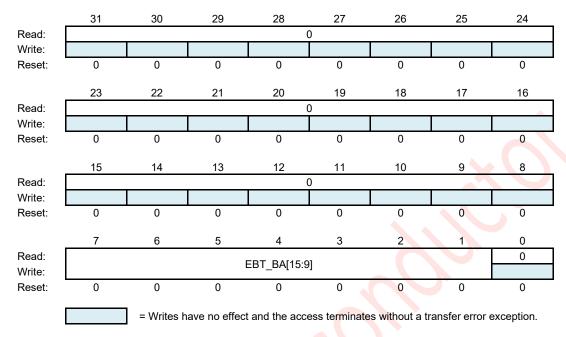

|    | 24.5.2. Register Descriptions                                       |     |

|    | 24.6. Function Description                                          | 333 |

|    | 24.6.1. Data Structure                                              | 333 |

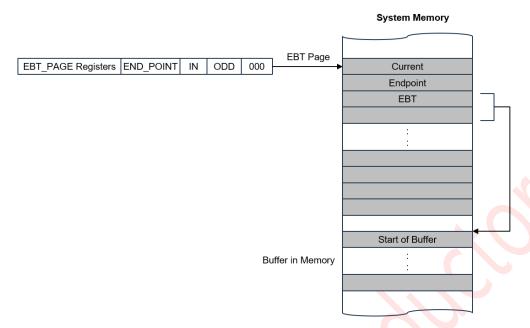

|    | 24.6.2. Endpoint Buffer Table                                       | 333 |

|    | 24.6.3. Rx vs. Tx As A USB Target Device                            | 334 |

|    | 24.6.4. Addressing Endpoint Buffer Table Entries                    |     |

|    | 24.6.5. Endpoint Buffer Table Formats                               |     |

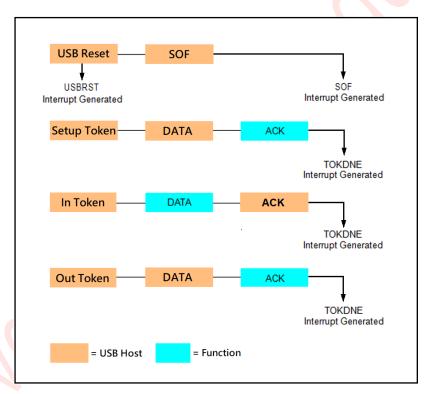

|    | 24.6.6. USB Transaction                                             |     |

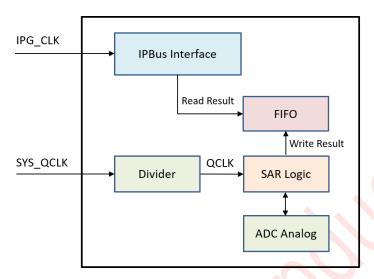

| 25 | . Analog-to-Digital Converter (ADC)                                 | 340 |

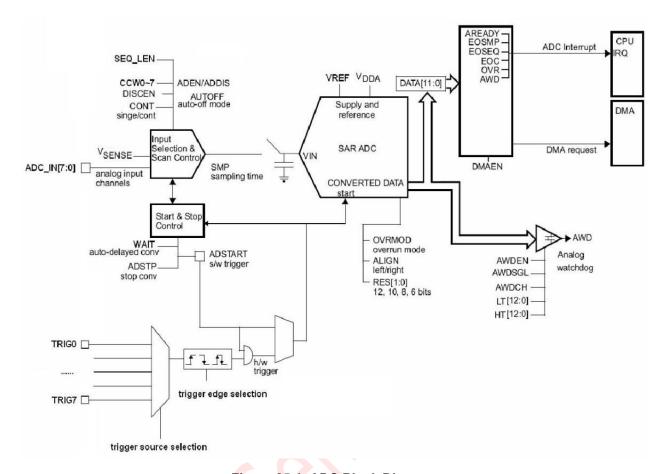

|    | 25.1. Introduction                                                  | 340 |

|    | 25.2. ADC Main Features                                             | 340 |

|    | 25.3. ADC Functional Description                                    | 341 |

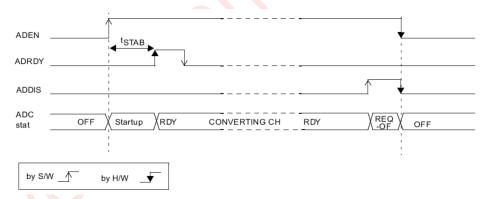

|    | 25.3.1. ADC On-Off Control (ADEN, ADDIS, ADRDY)                     |     |

|    | 25.3.2. ADC Clock                                                   |     |

|    | 25.3.3. Configuring The ADC                                         | 343 |

|    | 25.3.4. Channel Selection (CCWi)                                    |     |

|    | 25.3.5. Programmable Sampling Time (SMP)                            | 344 |

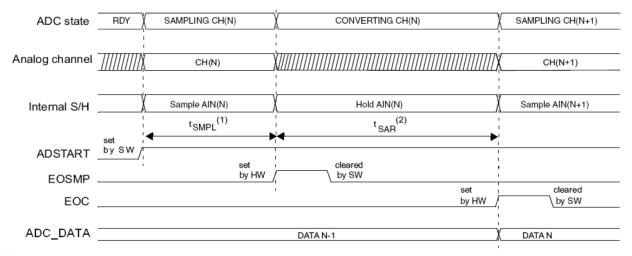

|    | 25.3.6. Single Conversion Mode (CONT = 0)                           | 344 |

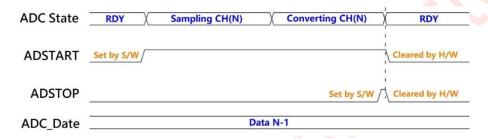

|    | 25.3.7. Continuous Conversion Mode (CONT = 1)                       | 345 |

|    | 25.3.8. Starting Conversions (ADSTART)                              | 345 |

|    | 25.3.9. Timings                                                     | 346 |

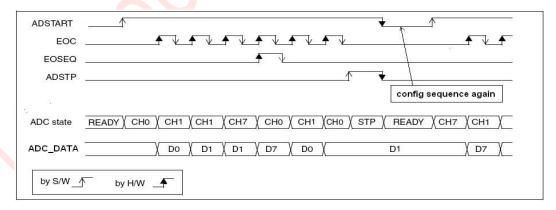

|    | 25.3.10. Stopping An Ongoing Conversion (ADSTP)                     | 347 |

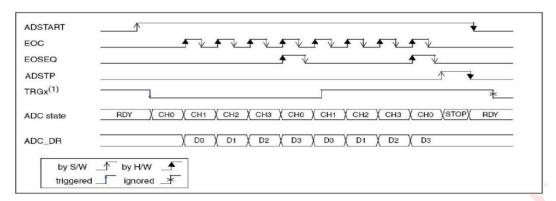

|    | 25.4. Conversion On External Trigger And Trigger Polarity           | 347 |

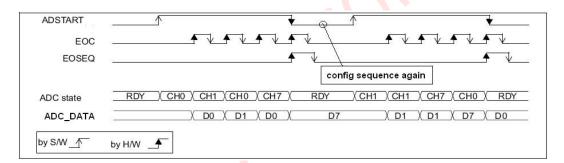

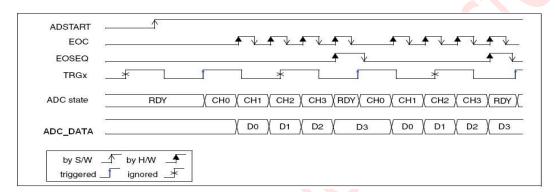

|    | 25.4.1. Discontinuous Mode (DISCEN)                                 | 349 |

|    | 25.4.2. Programmable Resolution (RES) - Fast Conversion Mode        | 349 |

|    | 25.4.3. End of Conversion, End of Sampling Phase (EOC, EOSMP Flags) | 350 |

|    | 25.4.4. End Of Conversion Sequence (Eoseq Flag)                     | 350 |

|    | 25.4.5. Example Timing Diagrams                                     | 350 |

|    | 25.5. Data Management                                               | 352 |

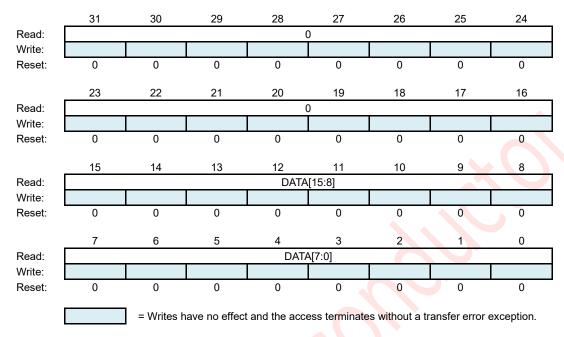

|    | 25.5.1. Data FIFO & Data Alignment (ADC_FIFO, ALIGN)                | 352 |

|    | 25.5.2. ADC Overrun (OVR, OVRMOD)                                   |     |

|    |                                                                     |     |

|    | 25.5.3. Managing A Sequence Of Data Converted Without Using The DMA   | . 353 |

|----|-----------------------------------------------------------------------|-------|

|    | 25.5.4. Managing Converted Data Without Using The DMA Without Overrun | . 353 |

|    | 25.5.5. Managing Converted Data Using The DMA                         | . 353 |

|    | 25.6. Low Power Features                                              | .354  |

|    | 25.6.1. Wait Mode Conversion                                          |       |

|    | 25.6.2. Auto-off Mode (AUTOFF)                                        | . 354 |

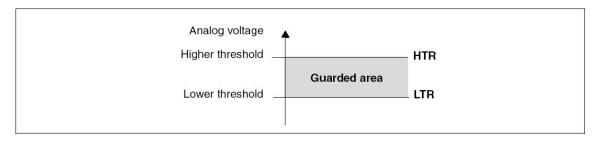

|    | 25.7. Analog Window Watchdog (AWD)                                    | .354  |

|    | 25.8. Temperature Sensor                                              | .355  |

|    | 25.9. ADC Interrupts                                                  | .355  |

|    | 25.10. Memory Map and Registers                                       | .356  |

|    | 25.10.1. Memory Map                                                   | . 356 |

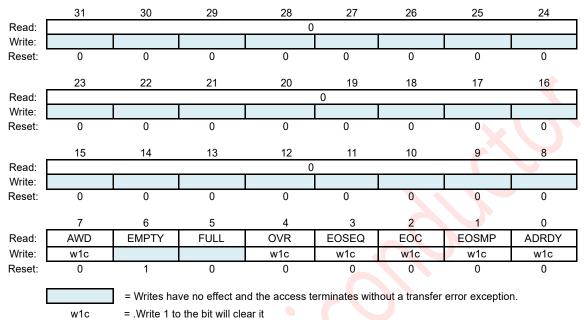

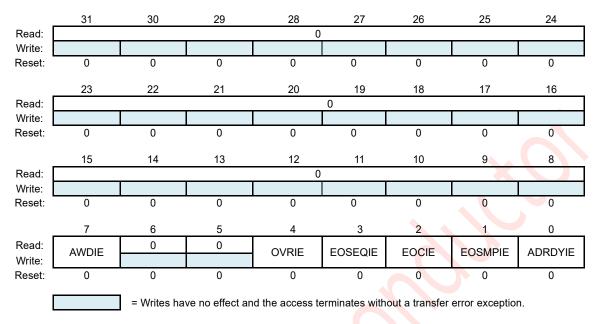

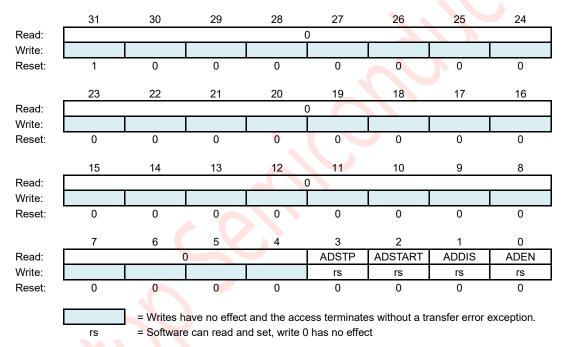

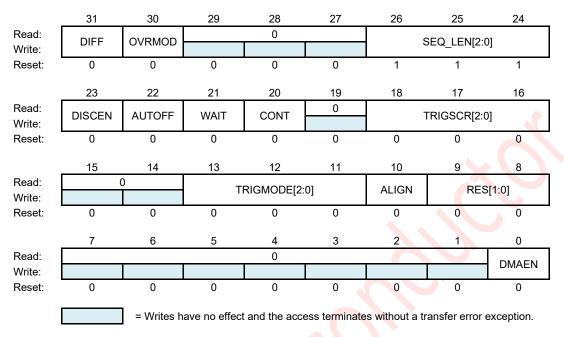

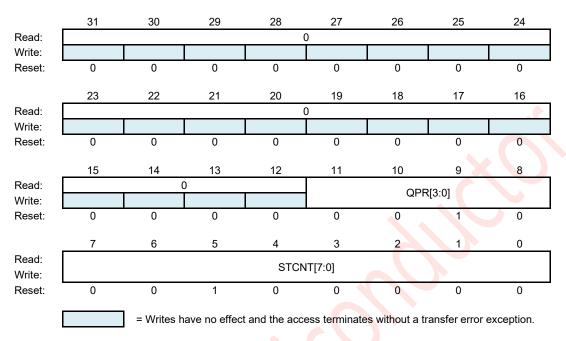

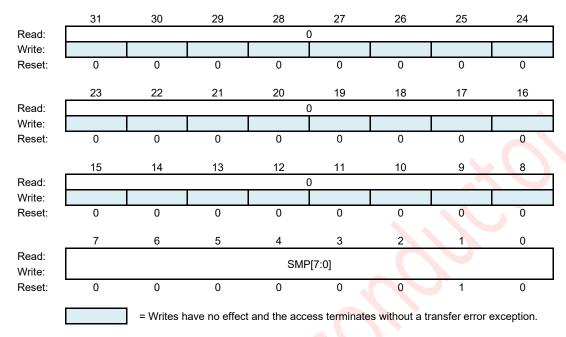

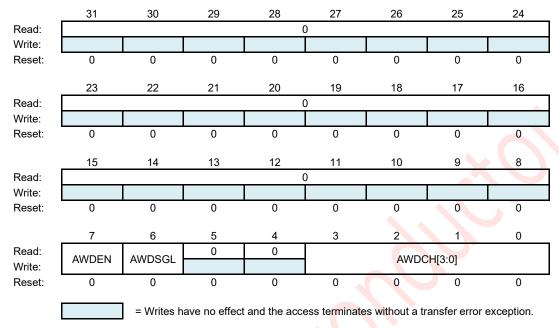

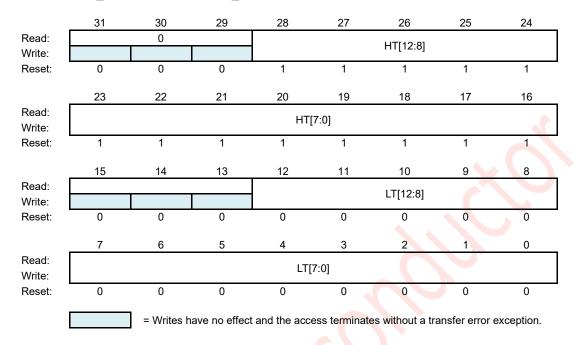

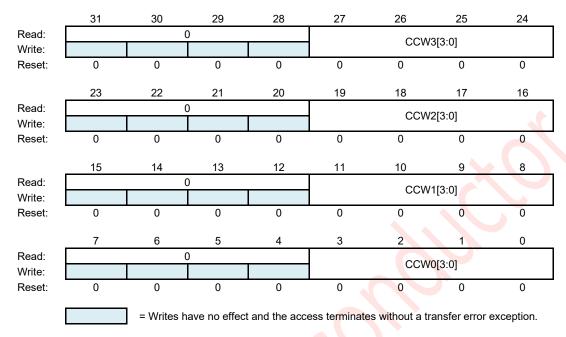

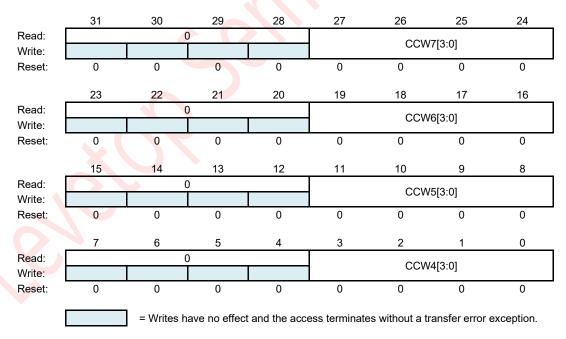

|    | 25.10.2. Register Descriptions                                        |       |

| 26 | TFT LCD Controller's Registers                                        | 370   |

|    | 26.1. PWM Control Register                                            |       |

|    | 26.2. GPIO Register                                                   | .374  |

| 27 | Electrical Characteristics                                            | 376   |

|    | 27.1. Absolute Maximum Ratings                                        | .376  |

|    | 27.2. DC Electrical Parameter                                         | .376  |

|    | 27.3. ESD Protection                                                  |       |

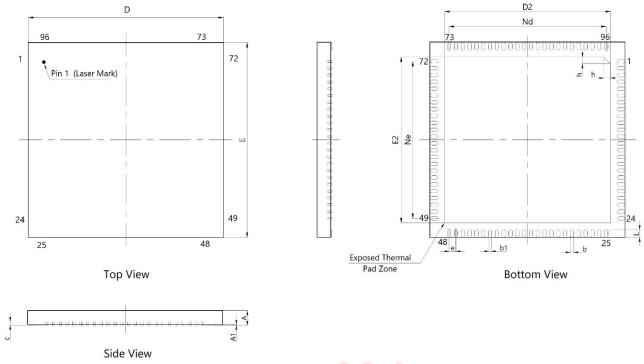

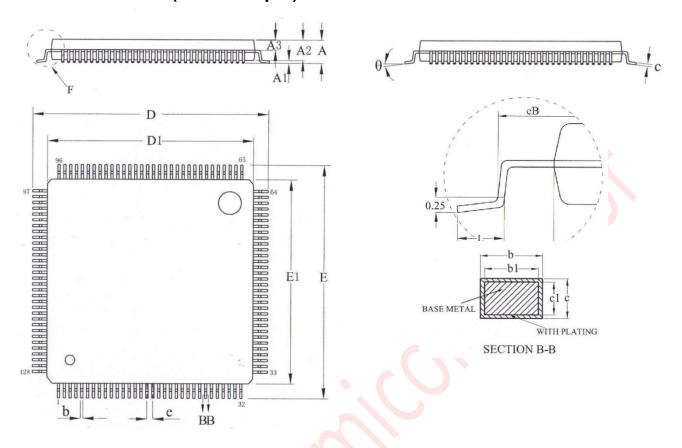

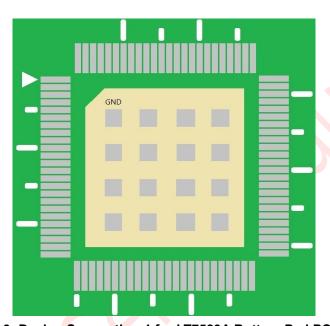

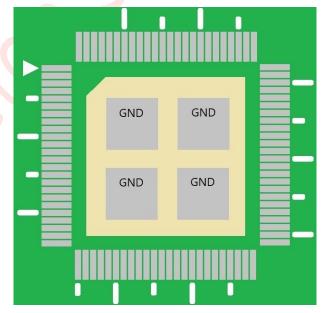

| 28 | Package Information                                                   | 379   |

|    | 28.1. LT7589A (QFN-96pin)                                             |       |

|    | 28.2. LT7589B (LQFP-128pin)                                           | .380  |

|    | 28.3. LT7589A PCB Layout Suggestions                                  | .381  |

| 29 | Application Circuit                                                   | 382   |

## Figure List

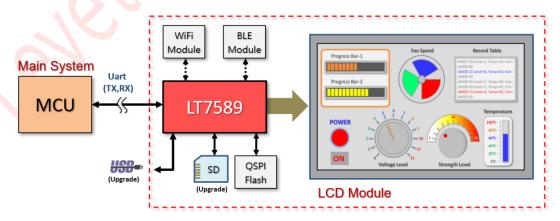

| Figure 1-1: LT7589 Designed on TFT Module                                               | 22 |

|-----------------------------------------------------------------------------------------|----|

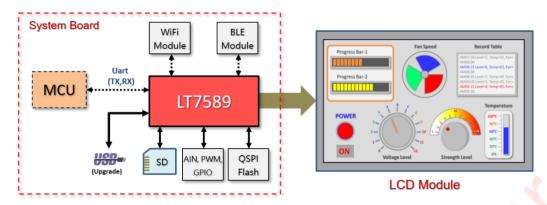

| Figure 1-2: LT7589 Designed on System Board                                             | 23 |

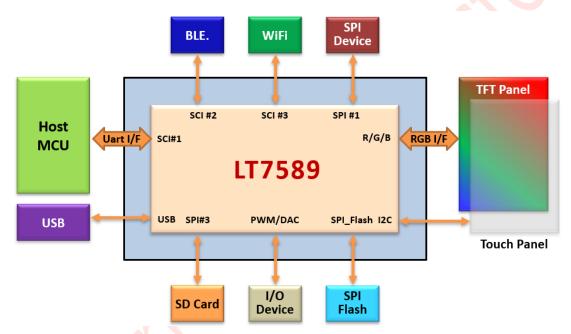

| Figure 1-3: LT7589 Application Architecture                                             | 23 |

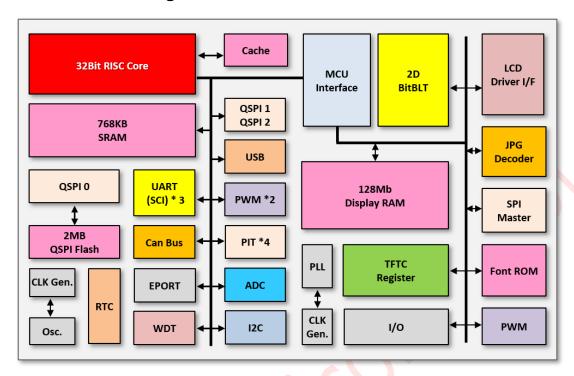

| Figure 1-4: LT7589 Internal Block Diagram                                               | 24 |

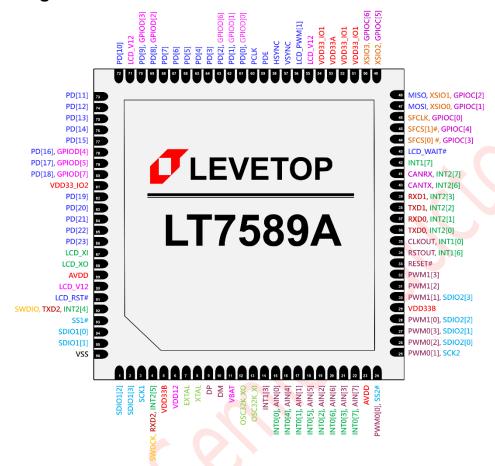

| Figure 2-1: LT7589A Pin Assignment (QFN-96Pin)                                          | 27 |

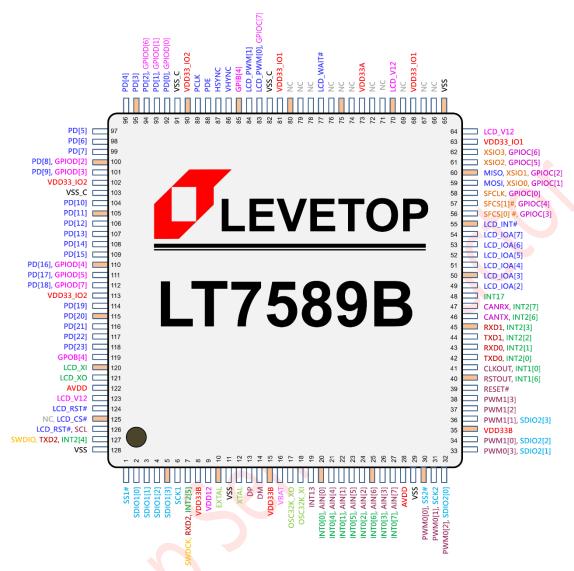

| Figure 2-2: LT7589B Pin Assignment (LQFP-128Pin)                                        | 28 |

| Figure 3-1: Communication Mode between LT7589 Internal MCU and TFT Graphics Accelerator | 43 |

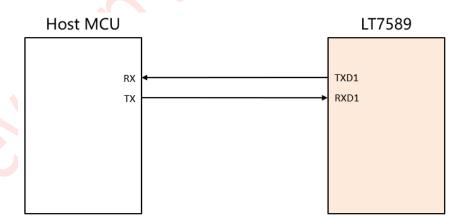

| Figure 3-2: Communication Mode with the Host MCU                                        | 43 |

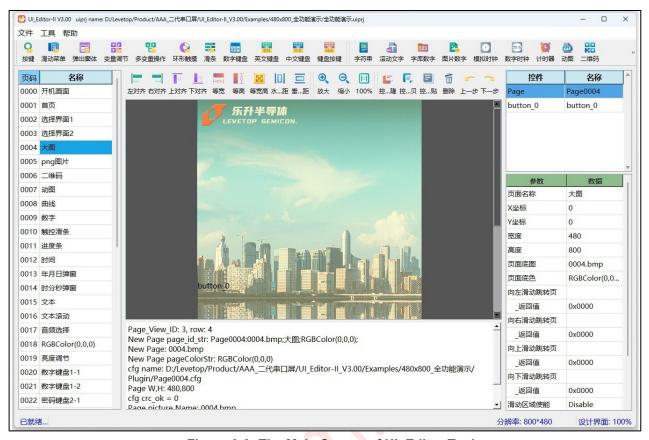

| Figure 3-3: The Main Screen of UI_Editor Tool                                           | 44 |

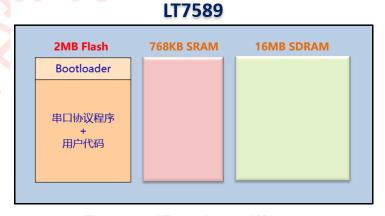

| Figure 3-4: LT7589 Internal Memory                                                      |    |

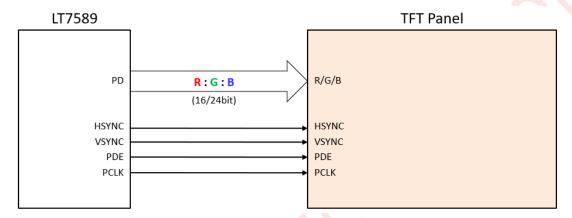

| Figure 3-5: Connection Between LT7589 and TFT LCD Panel                                 | 46 |

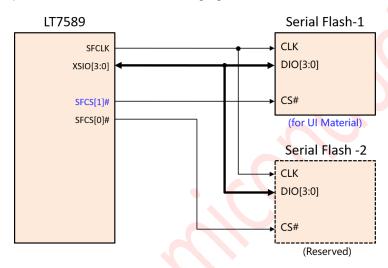

| Figure 3-6: Schematic Diagram of the Connection Between LT7589 and QSPI Flash           | 47 |

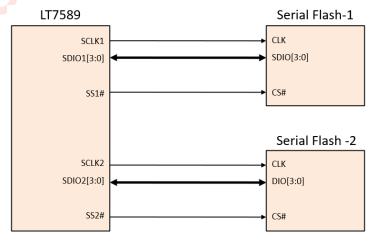

| Figure 3-7: Schematic Diagram of QSPI Flash Connection to LT7589 MCU End                | 47 |

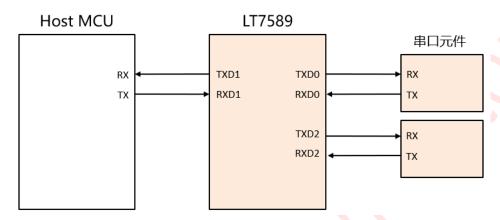

| Figure 3-8: LT7589 Provides Three Sets Of SCI Serial Ports                              | 48 |

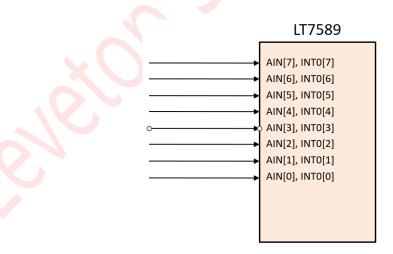

| Figure 3-9: LT7589 Provides Eight Analog Input                                          | 48 |

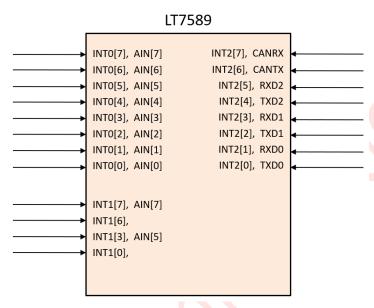

| Figure 3-10: The GPIO and Interrupt Input of MCU End                                    | 49 |

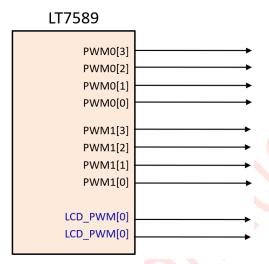

| Figure 3-11: PWM Output of LT7589 MCU End                                               | 50 |

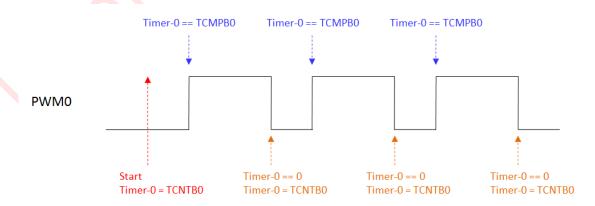

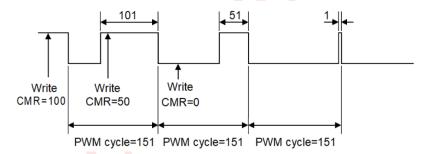

| Figure 3-12: LCD_PWM Waveform Diagram                                                   | 50 |

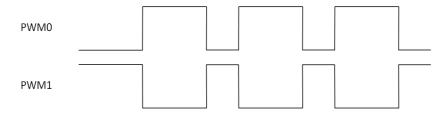

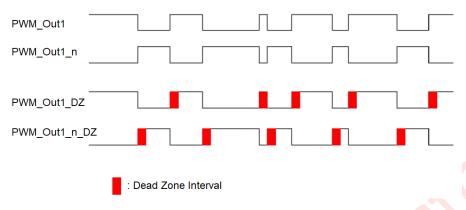

| Figure 3-13: LCD_PWM [0] and LCD_PWM [1] Complementary Outputs                          | 52 |

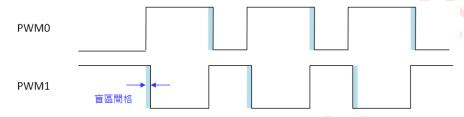

| Figure 3-14: LCD_PWM [0] and LCD_PWM [1] Complementary Output Blind Spot Timing         | 52 |

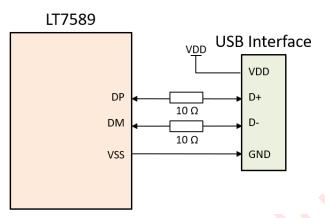

| Figure 3-15: LT7589 USB Interfa <mark>ce</mark>                                         | 53 |

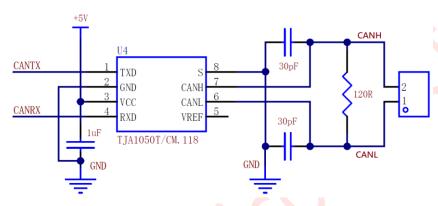

| Figure 3-16: Example of Canbus Interface Application                                    | 53 |

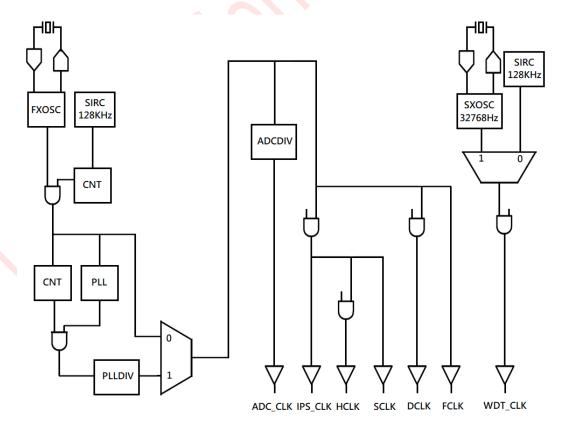

| Figure 3-17: Clock Signal Structure Diagram                                             | 54 |

| Figure 3-18: The TFT controller uses an external 12MHz crystal oscillator circuit       | 55 |

| Figure 3-19: LT7589 Reset Signal Structure Diagram                                      | 56 |

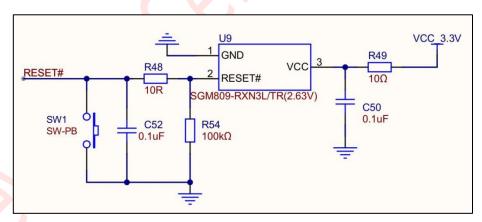

| Figure 3-20: Generate Reset Signal by Reset Chip                                        | 56 |

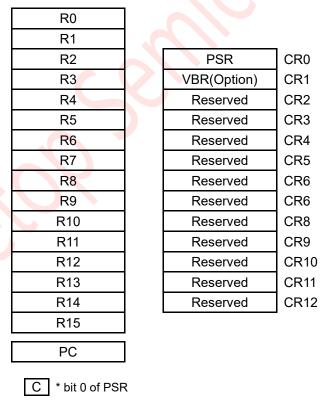

| Figure 4-1: Programming Model                                                           | 58 |

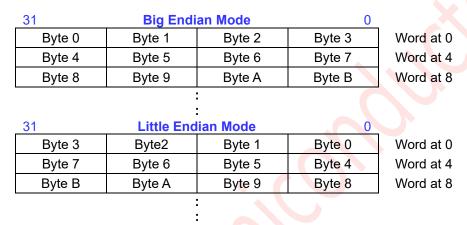

| Figure 4-2: Data Organization in Memory                                                 | 59 |

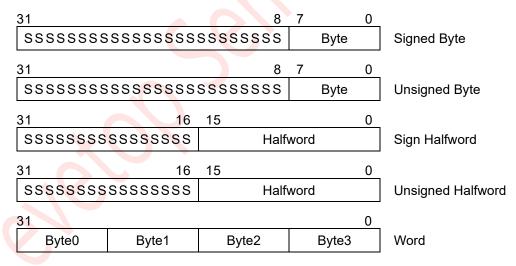

| Figur <mark>e 4-3: Data</mark> Organization in Registers                                | 59 |

| Figure 5-1: Address Map                                                                 | 63 |

| Figure 6-1: Wakeup Configuration Register (WKUPC)                                       | 66 |

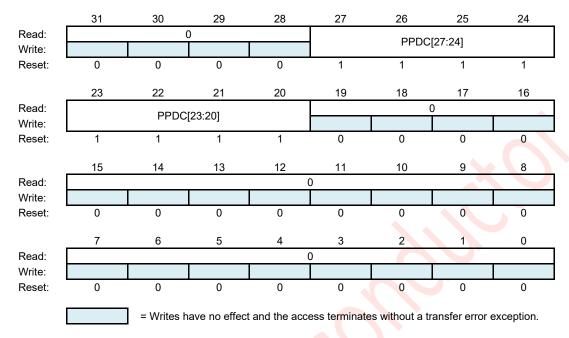

| Figure 6-2: Chip Pin Pull Down Configuration Register (CPPDC)                           | 68 |

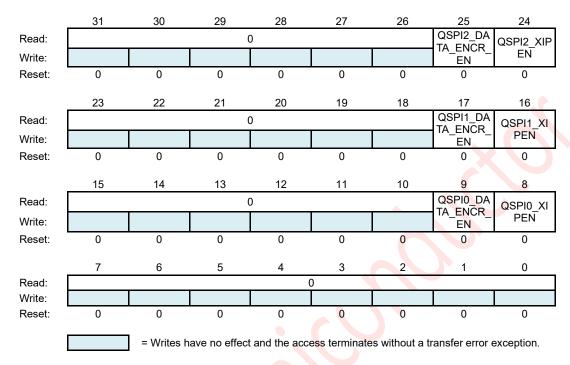

| Figure 6-3: QSPI XIP Mode Configuration Register (QSPIXIPMCFR)                          | 69 |

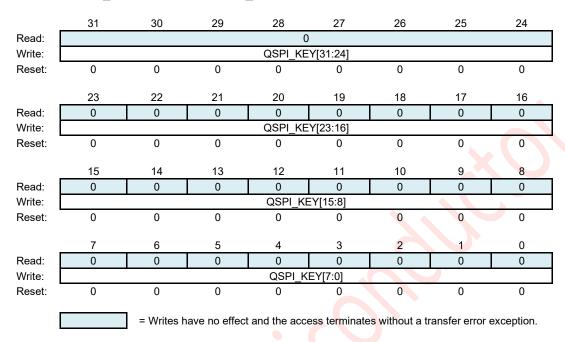

| Figure 6-4: QSPI 32-Bit Key Register (QSPILKEYR)                                        | 70 |

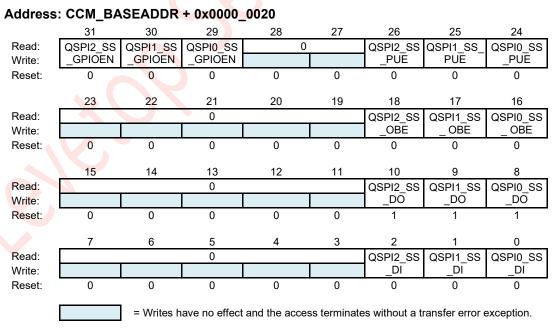

| Figure 6-5: QSPI GPIO Configuration Register (QSPIGPIOCR)                               | 70 |

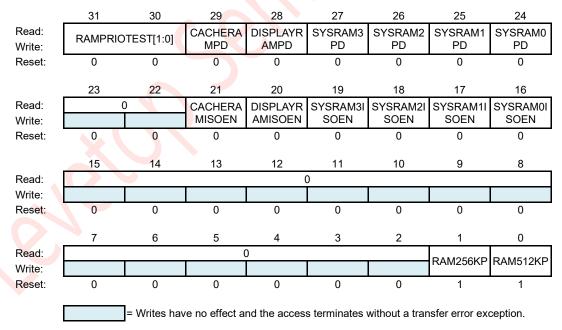

| Figure 6-6: MCU Access RAM Priority Configuration Register (MCURAMPRIOCR)               | 71 |

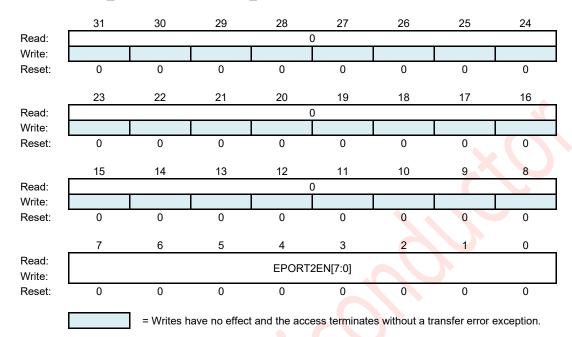

| Figure 6-7: EPORT2 Function Configuration Register (EPORT2FCR)                          | 73 |

| Figure 7-1: Interrupt Control Status Register (ICSR)                                    | 76 |

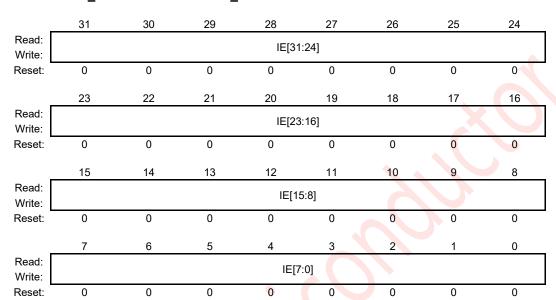

| Figure 7-2: Interrupt Enable Register (IER)                                    | 78  |

|--------------------------------------------------------------------------------|-----|

| Figure 7-3: Interrupt Pending Set Register (IPSR)                              | 79  |

| Figure 7-4: Interrupt Pending Clear Register (IPCR)                            | 80  |

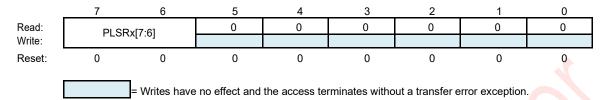

| Figure 7-5: Priority Level Select Registers (PLSR0-PLSR31)                     | 81  |

| Figure 7-6: System Priority Level Select Registers (SYSPLSR)                   | 82  |

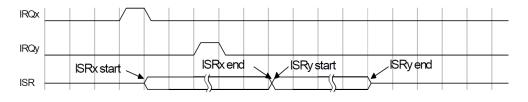

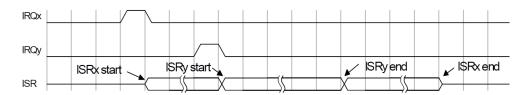

| Figure 7-7: One Pulse Interrupt without Confliction                            | 84  |

| Figure 7-8: Level-sensitive Interrupt without Confliction                      | 84  |

| Figure 7-9: Two Interrupts Occur at the Same Time                              | 84  |

| Figure 7-10: A lower Priority Interrupt Asserted with Confliction              | 85  |

| Figure 7-11: A higher Priority Interrupt Asserted with Confliction             | 85  |

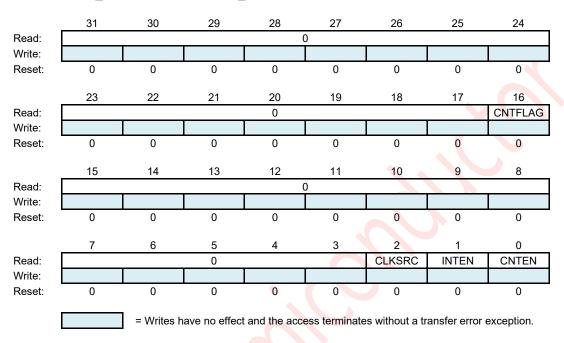

| Figure 8-1: EPT Control Status Register (EPTCSR)                               | 92  |

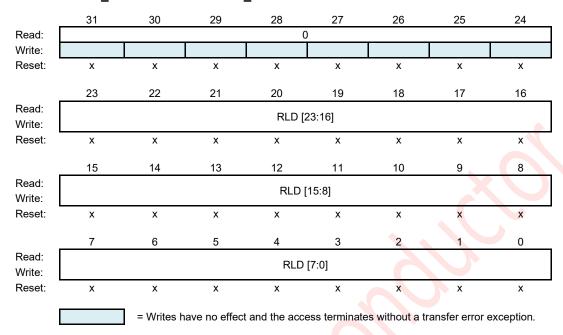

| Figure 8-2: EPT Reload Register (EPTRLD)                                       | 93  |

| Figure 8-3: EPT Counter Register (EPTCNT)                                      | 94  |

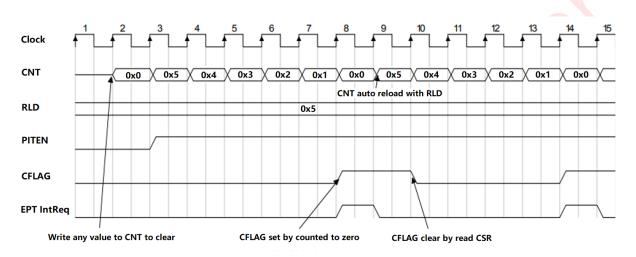

| Figure 8-4: EPT Count Timing                                                   | 95  |

| Figure 9-1: Clock Structure                                                    | 96  |

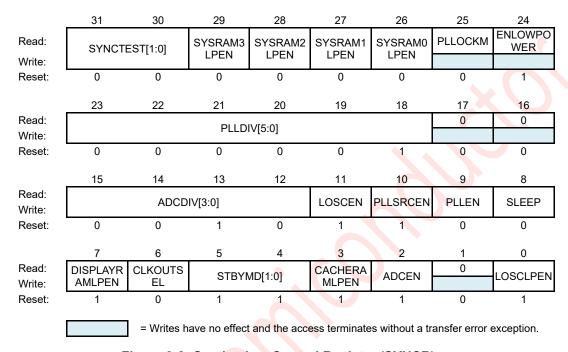

| Figure 9-2: Synthesizer Control Register (SYNCR)                               | 99  |

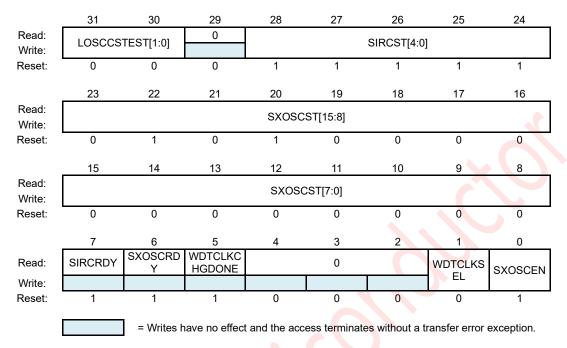

| Figure 9-3: Low Speed Oscillator Control and Status Register (LOSCCSR)         | 103 |

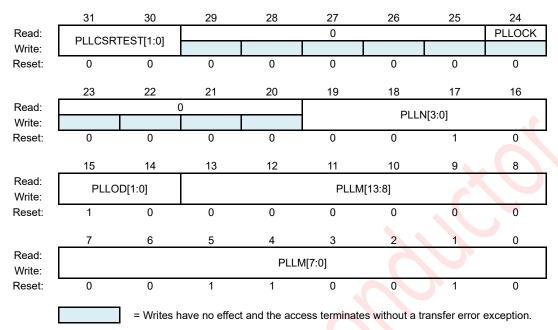

| Figure 9-4: PLL Configuration and Status Register (PLLCSR)                     |     |

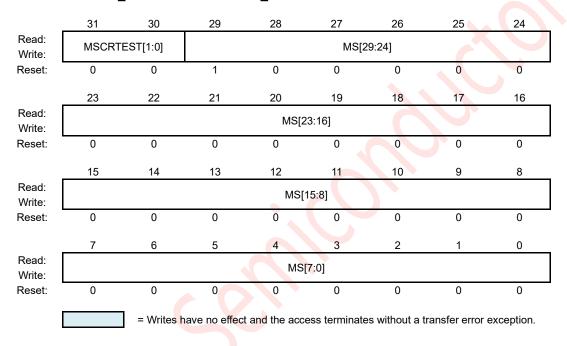

| Figure 9-5: Module Stop Control Register (MSCR)                                | 107 |

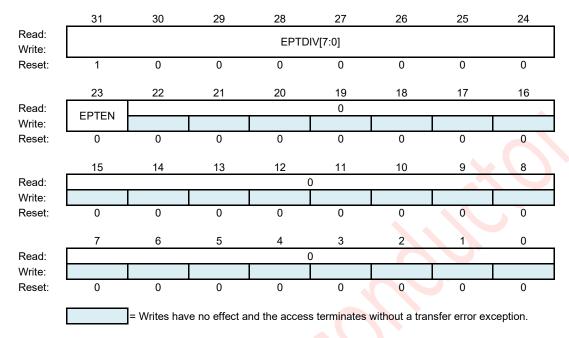

| Figure 9-6: EPT External Clock Source Enable Control Register (ECSECR)         | 109 |

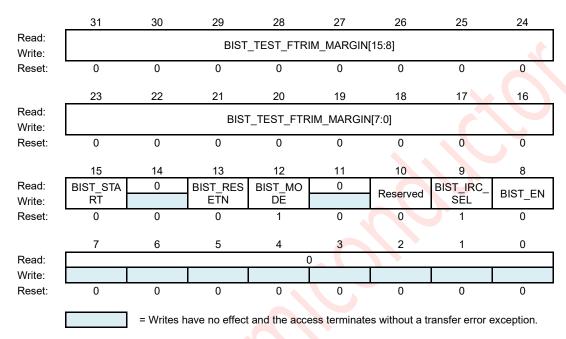

| Figure 9-7: OSC Bist Test Configuration Register1 (OBTCR1)                     | 110 |

| Figure 9-8: OSC Bist Test Configuration Register2 (OBTCR2)                     | 111 |

| Figure 9-9: OSC Bist Test Control Register (OBTCTLR)                           | 112 |

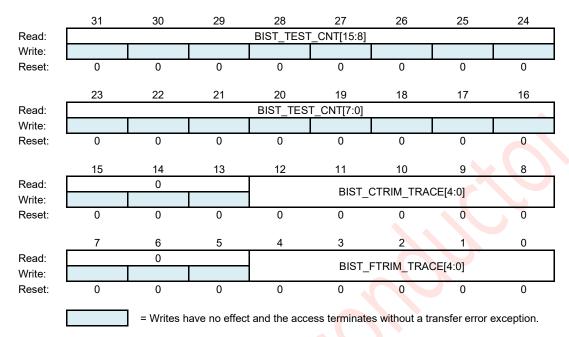

| Figure 9-10: OSC BIST Test Counter Register (OBTCNTR)                          | 113 |

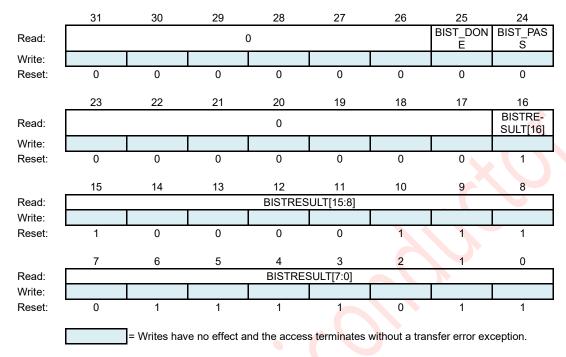

| Figure 9-11: OSC BIST Test Result Register (OBTRR)                             | 114 |

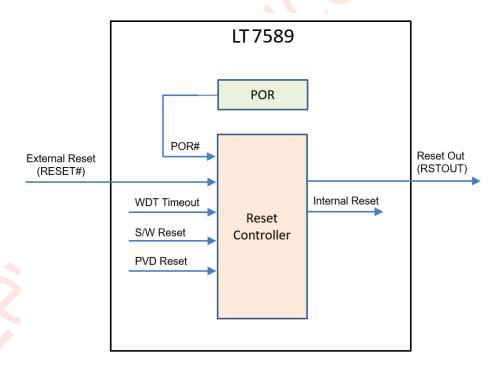

| Figure 10-1: Reset Controller Block Diagram                                    | 116 |

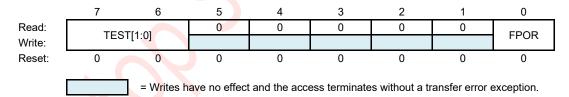

| Figure 10-2: Reset Test Register (RTR)                                         | 117 |

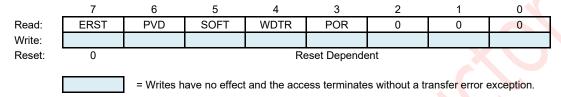

| Figure 10-3: Reset Status Register (RSR)                                       | 118 |

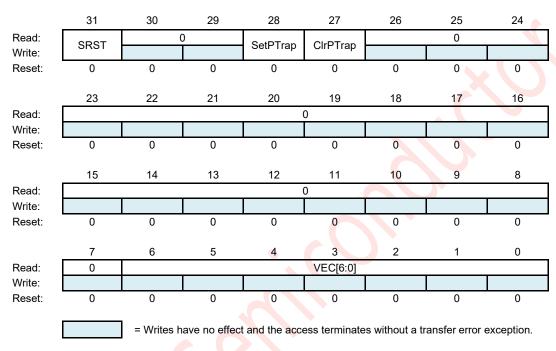

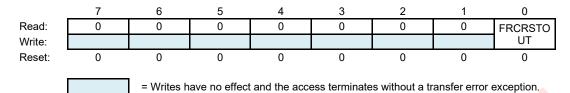

| Figure 10-4: Reset Control Register (RCR)                                      | 119 |

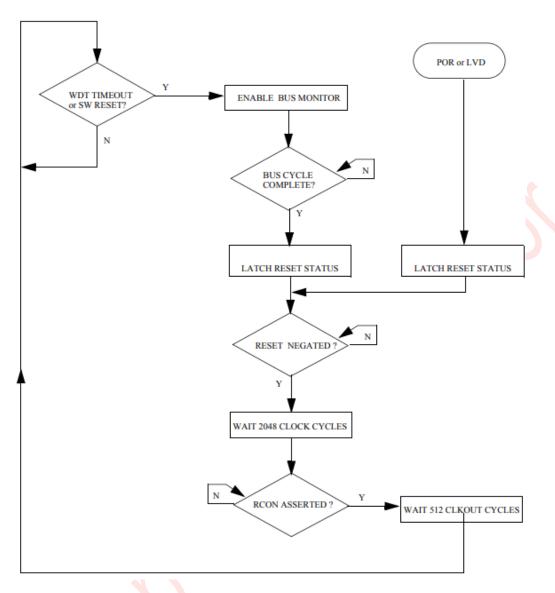

| Figure 10-5: Reset Control Flow                                                | 121 |

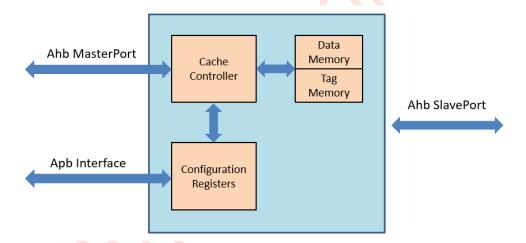

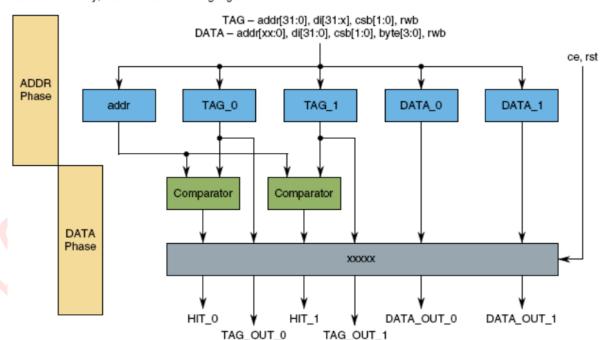

| Figure 12-1: Cache Module Block Diagram                                        | 124 |

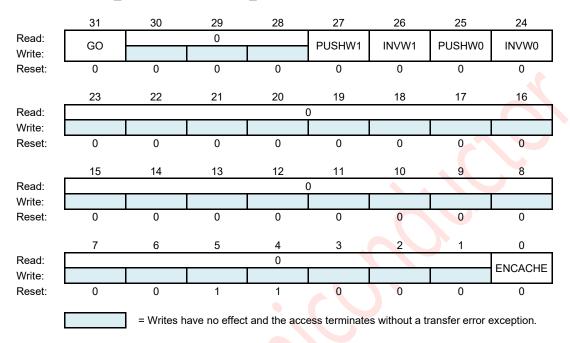

| Figure 12-2: Cache Control Register (LMEM_CCR)                                 | 126 |

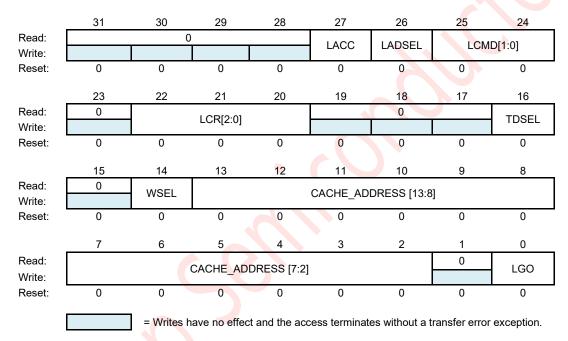

| Figure 12-3: Cache Line Control Register (LMEM_CLCR)                           | 127 |

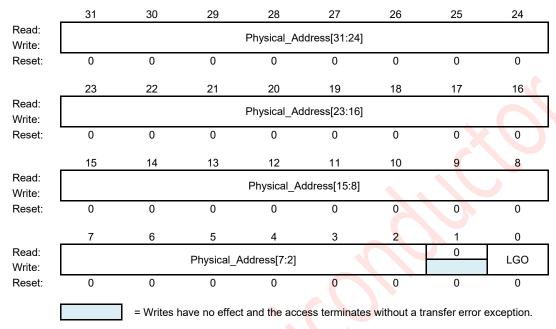

| Figure 12-4: Cache Search Address Register (LMEM_CSAR)                         | 129 |

| Figure 12-5: Cache Read/Write Value Register (LMEM_CCVR)                       | 130 |

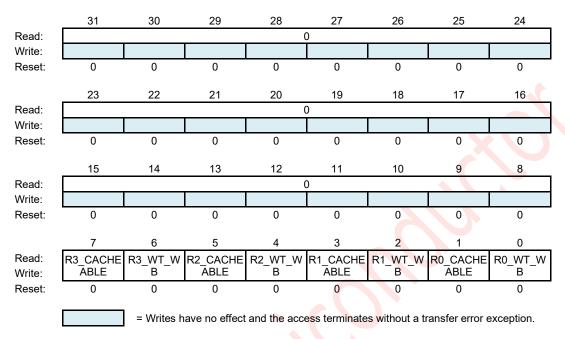

| Figure 12-6: Cache Access Register (LMEM_ACRG)                                 | 131 |

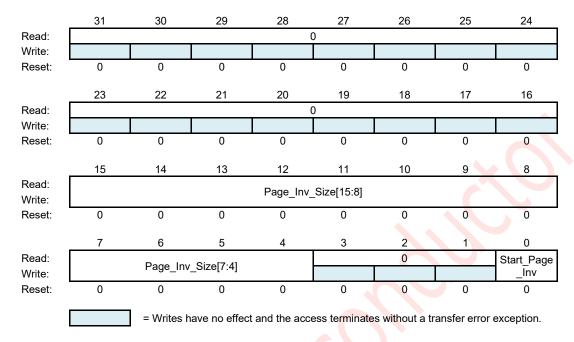

| Figure 12-7: Cache Page Invalidate Base Address Register (LMEM_PAGE_INV_BADDR) | 132 |

| Figure 12-8: Cache Page Invalidate Size Register (LMEM_PAGE_INV_SIZE)          | 133 |

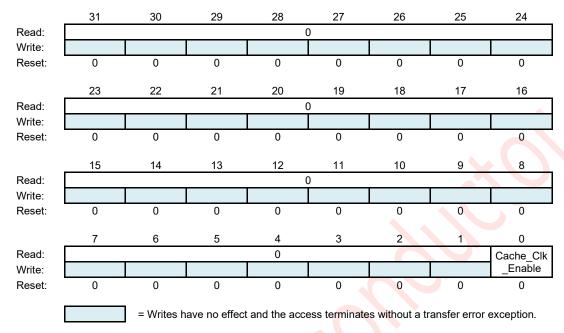

| Figure 12-9: Cache Clock Enable Register (LMEM_CACHE_CLK_EN)                   | 134 |

| Figure 12-10: Cache Tag and Data Access Structure                              | 135 |

| Figure 13-1: DMA Block Diagram                                                          | 142 |

|-----------------------------------------------------------------------------------------|-----|

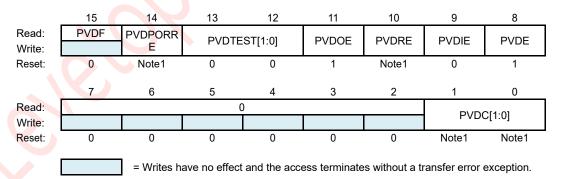

| Figure 14-1: Programmable Voltage Detector Configuration Register (PVDC)                | 144 |

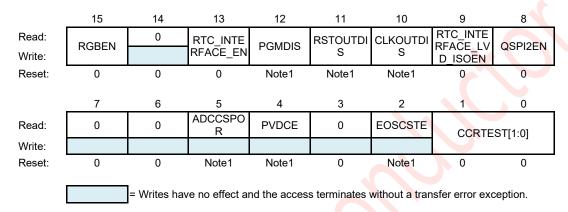

| Figure 14-2: Customer Configuration Register (CCR)                                      | 146 |

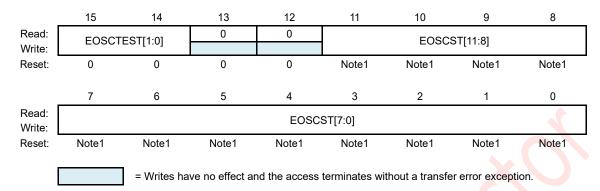

| Figure 14-3: External High Speed Oscillator Stable Time Configuration Register (EOSCST) | 149 |

| Figure 14-4: PLL Lock Time Configuration Register (PLLOCKCR)                            | 150 |

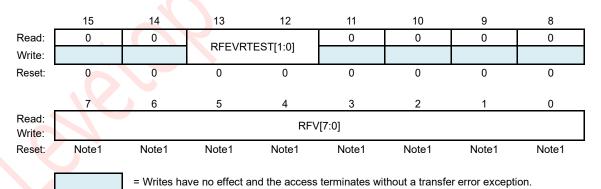

| Figure 14-5: RESET Pin Filter Enable and Value Register (RFEVR)                         | 150 |

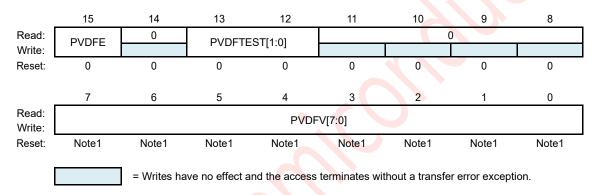

| Figure 14-6: Programmable Voltage Detector Filter Enable and Value Register (PVDFEVR)   | 151 |

| Figure 14-7: Factory Configuration Register (FCR)                                       | 152 |

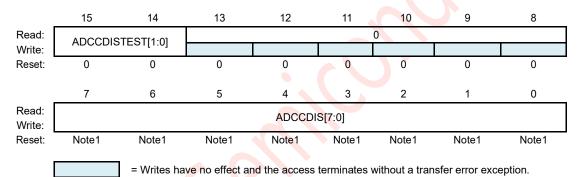

| Figure 14-8: ADC Channel Disable Configuration Register (ADCCDISR)                      | 153 |

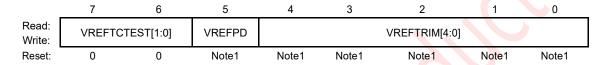

| Figure 14-9: VREF Trimming Configuration Register (VREFTCR)                             | 154 |

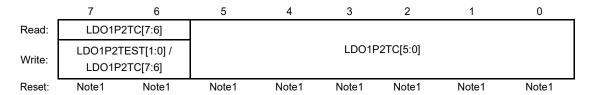

| Figure 14-10: LDO1P2 Trimming Configuration Register (LDOTCR)                           | 155 |

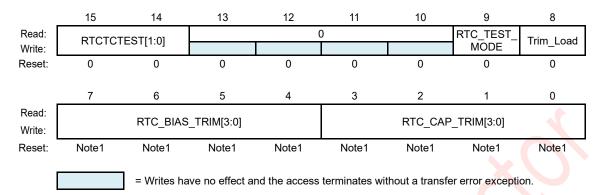

| Figure 14-11: RTC Trimming Configuration Register (RTCTCR)                              | 156 |

| Figure 15-1: PIT Block Diagram                                                          | 157 |

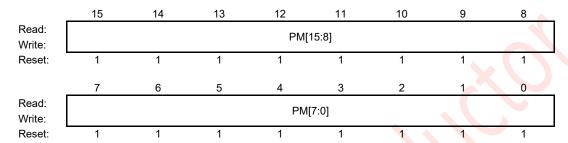

| Figure 15-2: PIT Modulus Register (PMR)                                                 | 159 |

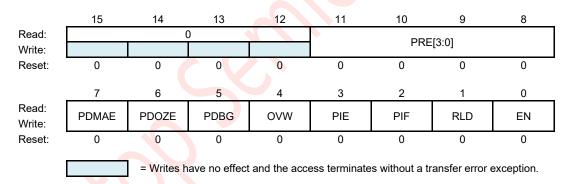

| Figure 15-3: PIT Control and Status Register (PCSR)                                     | 159 |

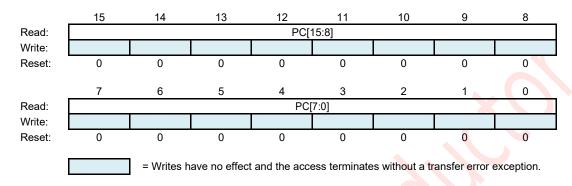

| Figure 15-4: PIT Count Register (PCNTR)                                                 | 162 |

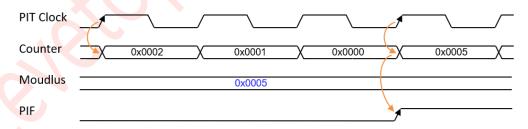

| Figure 15-5: Counter Reloading from the Modulus Latch                                   | 162 |

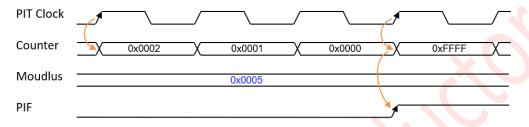

| Figure 15-6: Counter in Free-Running Mode                                               |     |

| Figure 16-1: Watchdog Timer Block Diagram                                               | 165 |

| Figure 16-2: Watchdog Modulus Register (WMR)                                            | 166 |

| Figure 16-3: Watchdog Control Register (WCR)                                            | 167 |

| Figure 16-4: Watchdog Service Register (WSR)                                            | 169 |

| Figure 16-5: Watchdog Count Register (WCNTR)                                            | 169 |

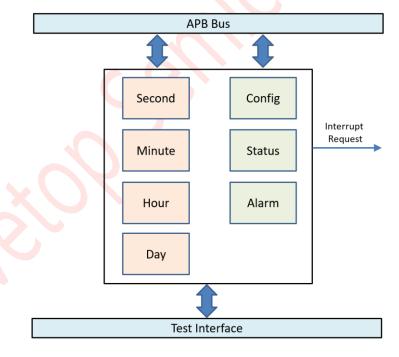

| Figure 17-1: RTC Block Diagram                                                          | 170 |

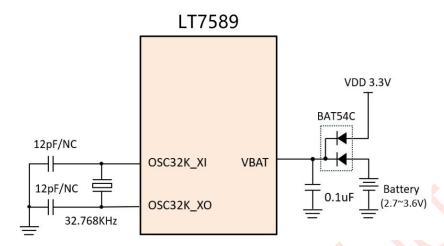

| Figure 17-2: RTC Application Circuit                                                    | 171 |

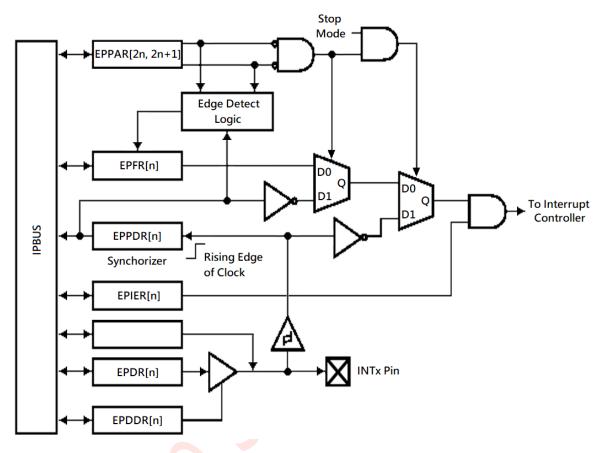

| Figure 18-1: EPORT Block Diagram                                                        |     |

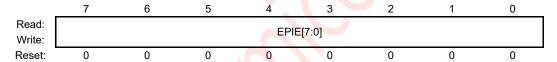

| Figure 18-2: EPORT Port Interrupt Enable Register (EPIER)                               | 174 |

| Figure 18-3: EPORT Data Direction Register (EPDDR)                                      | 175 |

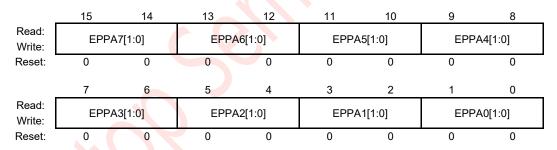

| Figure 18-4: EPORT Pin Assignment Register (EPPAR)                                      | 175 |

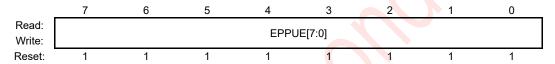

| Figure 18-5: EPORT Pin Pull-up enable Register (EPPUE)                                  | 176 |

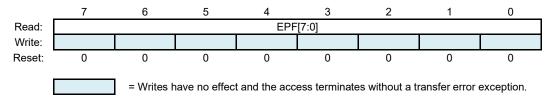

| Figure 18-6: EPORT Port Flag Register (EPFR)                                            | 177 |

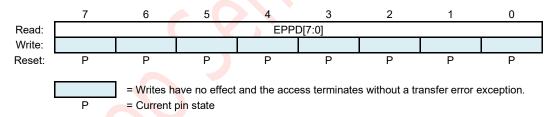

| Figure 18-7: EPORT Port Pin Data Register (EPPDR)                                       | 177 |

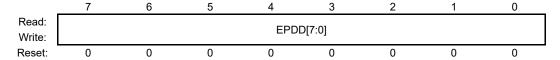

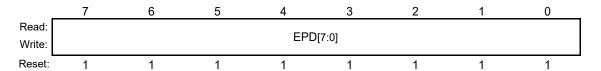

| Figure 18-8: EPORT Port Data Register (EPDR)                                            | 178 |

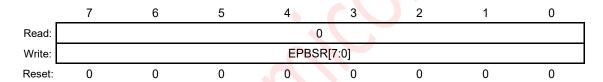

| Figure 18-9: EPORT Port Bit Set Register (EPBSR)                                        | 178 |

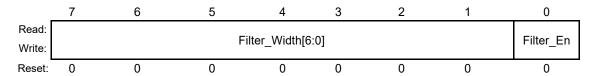

| Figure 18-10: EPORT Digital Filter Control Register (EPFC)                              | 179 |

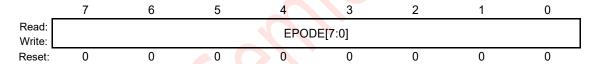

| Figure 18-11: EPORT Open Drain Enable Register (EPODE)                                  | 179 |

| Figure 18-12: EPORT Level Polarity Register (EPLPR)                                     | 180 |

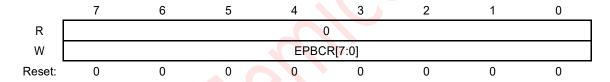

| Figure 18-13: EPORT Port Bit Clear Register (EPBCR)                                     | 180 |

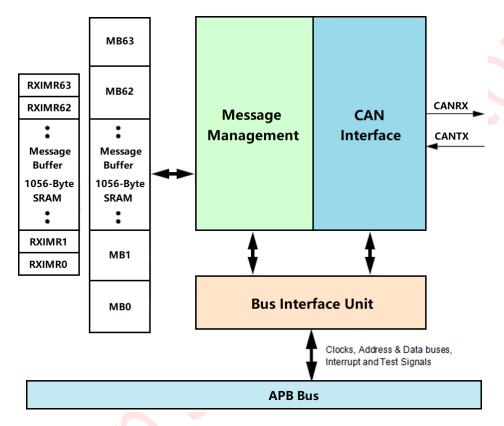

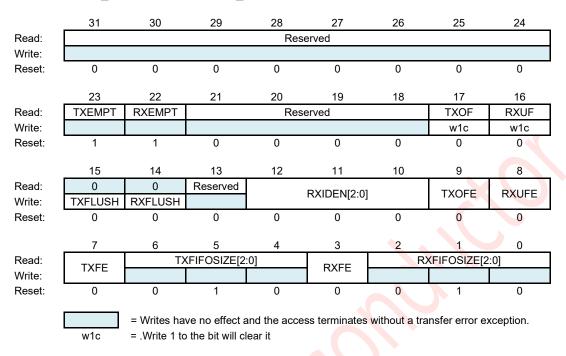

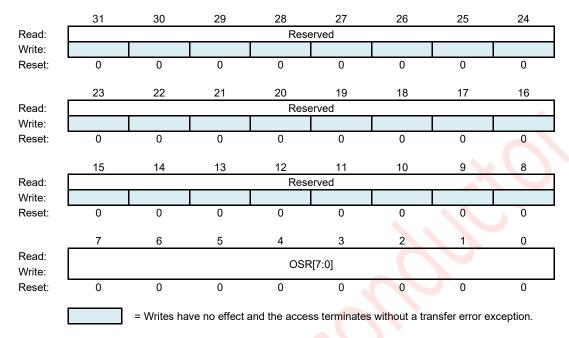

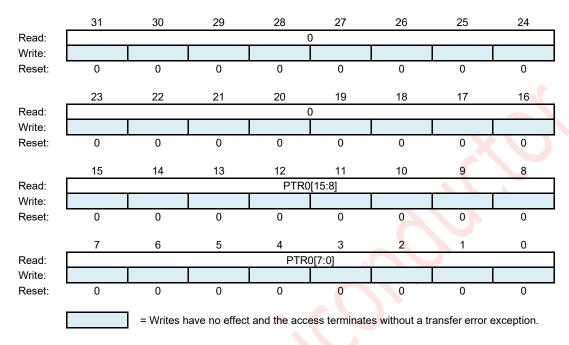

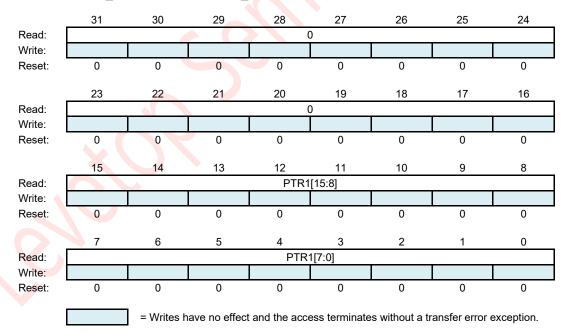

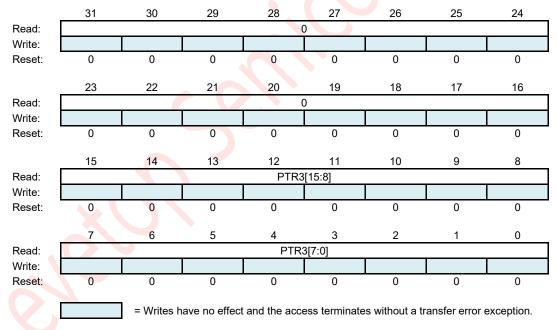

| Figure 19-1: CANBus Block Diagram                                                       | 181 |