# LT7589

## Uart TFT 显示控制芯片

*High Performance Uart TFT Display Controller*

---

## 规 格 书

V1.3

[www.levetop.cn](http://www.levetop.cn)

乐升半导体有限公司

## 版本记录

| 版本   | 日期         | 描述                                                                                                                   |

|------|------------|----------------------------------------------------------------------------------------------------------------------|

| V1.0 | 2024/11/22 | <ul style="list-style-type: none"><li>● LT7589 初版</li></ul>                                                          |

| V1.1 | 2025/03/20 | <ul style="list-style-type: none"><li>● 原理图更新</li><li>● VDD33_IO Pin 脚说明更新</li></ul>                                 |

| V1.2 | 2025/04/21 | <ul style="list-style-type: none"><li>● 更新引脚 LCD_XI 的说明</li><li>● 更新表 6-4: 外部串行 Flash 信号说明</li><li>● 原理图更新</li></ul> |

| V1.3 | 2025/11/28 | <ul style="list-style-type: none"><li>● 更新表 28-1: QFN-96Pin 尺寸参数</li><li>● 更新图 29-2: LT7589B 参考原理图</li></ul>         |

## 版权说明

本文件之版权属于 乐升半导体 所有，若需要复制或复印请事先得到 乐升半导体 的许可。本文件记载之信息虽然都有经过校对，但是 乐升半导体 对文件使用说明的规格不承担任何责任，文件内提到的应用程序仅用于参考，乐升半导体 不保证此类应用程序不需要进一步修改。乐升半导体 保留在不事先通知的情况下更改其产品规格或文件的权利。有关最新产品信息，请访问我们的网站 <Http://www.levetop.cn> 。

## 内 容

|                                  |    |

|----------------------------------|----|

| 版本记录 .....                       | 2  |

| 版权说明 .....                       | 2  |

| 内 容 .....                        | 3  |

| 图 列 表 .....                      | 13 |

| 表 列 表 .....                      | 20 |

| 1. 芯片介绍 .....                    | 23 |

| 1.1. 基本简介 .....                  | 23 |

| 1.2. 系统应用方块图 .....               | 23 |

| 1.3. 内部方块图 .....                 | 25 |

| 1.4. 功能简介 .....                  | 26 |

| 2. 引脚信号 .....                    | 28 |

| 2.1. 芯片脚位图 .....                 | 28 |

| 2.2. 信号说明 .....                  | 30 |

| 2.2.1. SCI (Uart) 串口信号 .....     | 30 |

| 2.2.2. LCD 屏接口信号 .....           | 31 |

| 2.2.3. QSPI 信号 .....             | 32 |

| 2.2.4. 外部串行 Flash 信号 .....       | 33 |

| 2.2.5. PWM 信号 .....              | 34 |

| 2.2.6. USB 信号 .....              | 35 |

| 2.2.7. GPIO 与中断信号 .....          | 36 |

| 2.2.8. ADC 模拟信号 .....            | 38 |

| 2.2.9. 其他控制信号 .....              | 38 |

| 2.2.10. 电源与时钟信号 .....            | 39 |

| 2.2.11. 使用不同 TFT 屏的 IO 口资源 ..... | 41 |

| 3. 串口屏功能说明 .....                 | 43 |

| 3.1. 串口通讯接口 .....                | 43 |

| 3.2. UI_Editor-III 串口屏协议表 .....  | 45 |

| 3.3. 二次开发 .....                  | 45 |

| 3.4. 芯片接口应用 .....                | 46 |

| 3.4.1. TFT LCD 屏的接口 .....        | 46 |

|                                                        |           |

|--------------------------------------------------------|-----------|

| 3.4.2. SSI (Synchronous Serial Interface) 串行接口.....    | 47        |

| 3.4.3. SCI (Serial Communication Interface) 串行接口 ..... | 48        |

| 3.4.4. ADC 模拟输入接口 .....                                | 48        |

| 3.4.5. GPIO 与中断输入接口 .....                              | 49        |

| 3.4.6. PWM 输出接口 .....                                  | 50        |

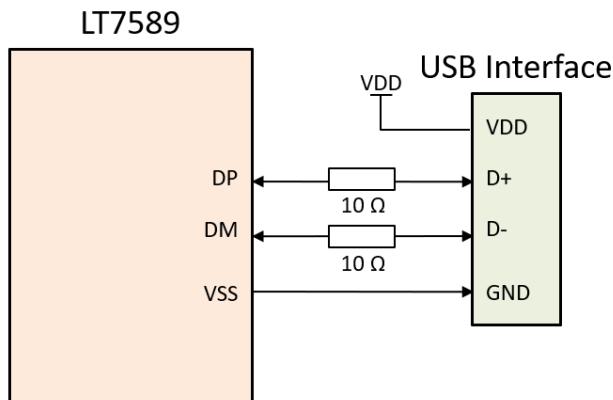

| 3.4.7. USB 接口 .....                                    | 53        |

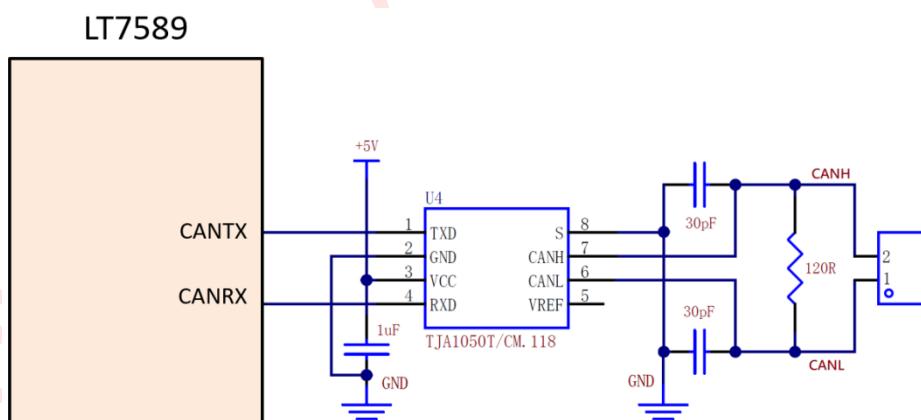

| 3.4.8. Canbus 接口 .....                                 | 53        |

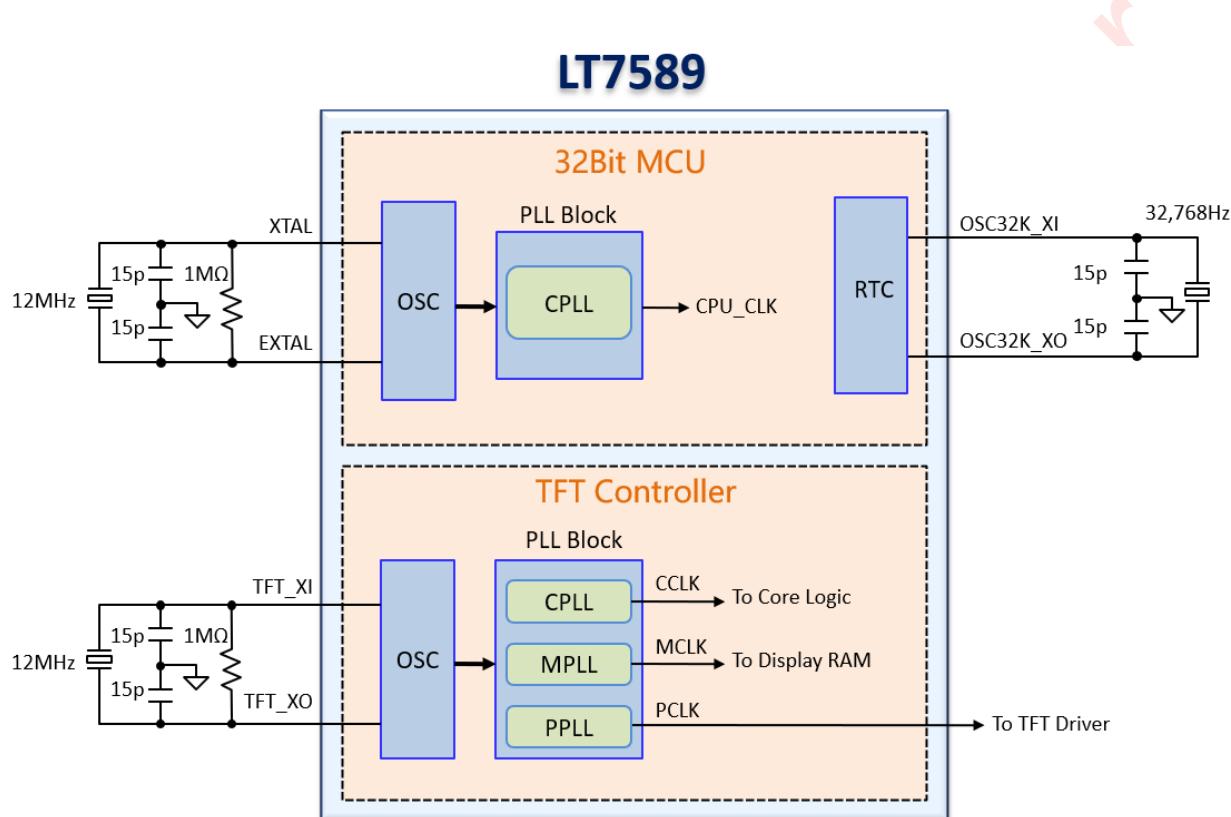

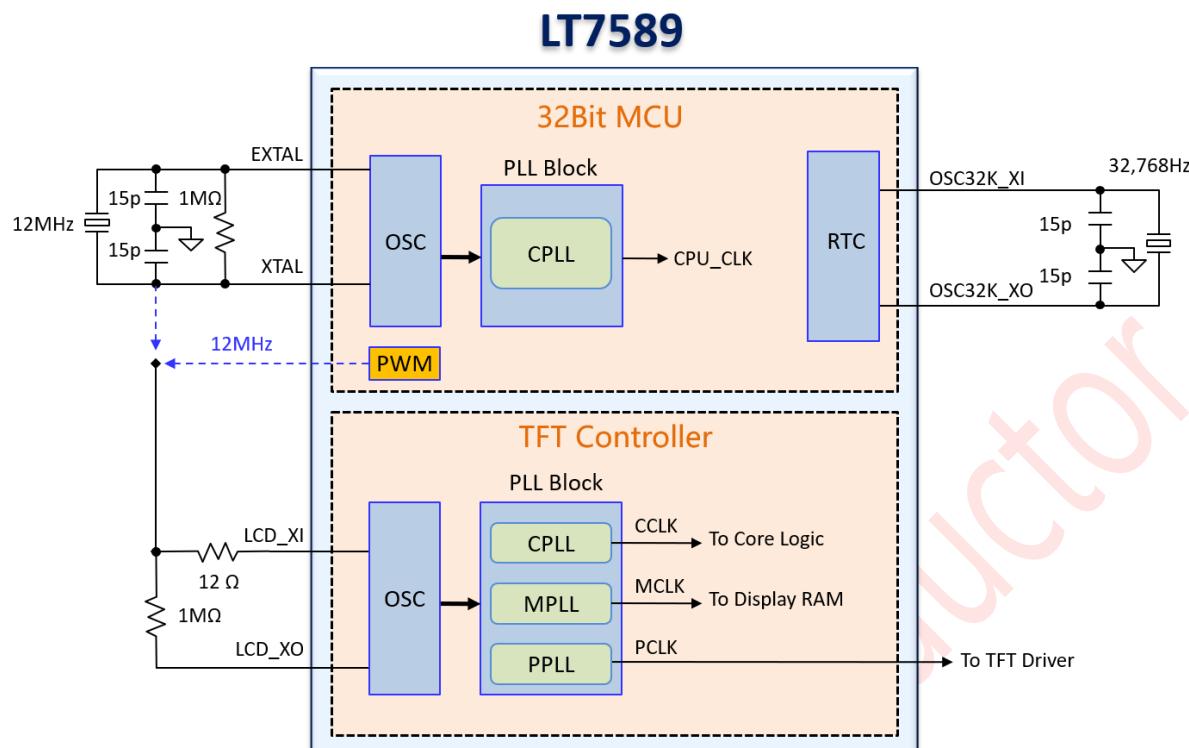

| 3.4.9. 时钟信号 .....                                      | 54        |

| 3.4.10. 复位信号 .....                                     | 56        |

| <b>4. 32 位 RISC 微处理器介绍 .....</b>                       | <b>57</b> |

| 4.1. 功能特点.....                                         | 57        |

| 4.2. 微体系结构总结 .....                                     | 57        |

| 4.3. 程序设计模型 .....                                      | 58        |

| 4.4. 数据格式汇总 .....                                      | 59        |

| 4.5. 操作和寻址能力 .....                                     | 60        |

| 4.6. 指令集概述 .....                                       | 60        |

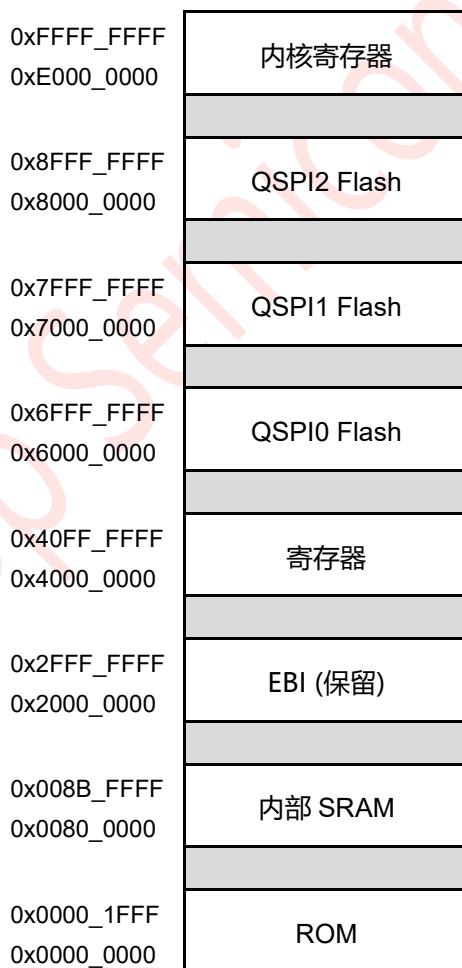

| <b>5. 内存与寄存器配置.....</b>                                | <b>63</b> |

| 5.1. 简要说明.....                                         | 63        |

| 5.2. 地址配置图 .....                                       | 63        |

| <b>6. 芯片配置模块 (CCM) .....</b>                           | <b>65</b> |

| 6.1. 基本介绍.....                                         | 65        |

| 6.2. 功能特点.....                                         | 65        |

| 6.3. 内存映射和寄存器 .....                                    | 65        |

| 6.3.1. 内存映射 .....                                      | 65        |

| 6.3.2. 寄存器描述.....                                      | 66        |

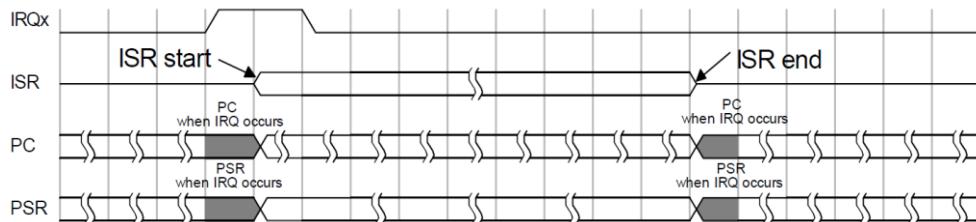

| <b>7. 嵌入式中断控制器 (EIC) .....</b>                         | <b>74</b> |

| 7.1. 基本介绍.....                                         | 74        |

| 7.2. 功能特点.....                                         | 74        |

| 7.3. 内存映射和寄存器 .....                                    | 74        |

| 7.3.1. 内存映射 .....                                      | 74        |

| 7.3.2. 寄存器描述.....                                      | 76        |

| 7.4. 功能描述.....                                         | 83        |

| 7.4.1. 无冲突的中断处理.....                                   | 84        |

|                              |     |

|------------------------------|-----|

| 7.4.2. 有冲突的中断 .....          | 84  |

| 7.4.3. 待定陷阱功能 .....          | 85  |

| 7.5. 中断来源 .....              | 86  |

| 8. 嵌入式可编程定时器 (EPT) .....     | 91  |

| 8.1. 基本介绍 .....              | 91  |

| 8.2. 内存映射和寄存器 .....          | 91  |

| 8.2.1. 内存映射 .....            | 91  |

| 8.2.2. 寄存器描述 .....           | 92  |

| 8.3. 功能描述 .....              | 95  |

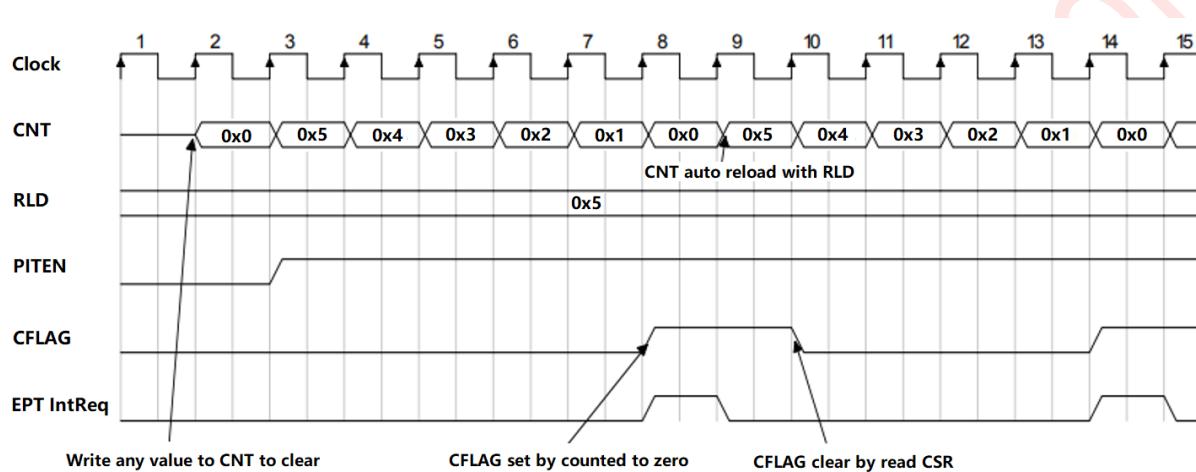

| 8.3.1. 计数时序 .....            | 95  |

| 9. 时钟和电源控制模块 (CLKPWRM) ..... | 96  |

| 9.1. 基本概述 .....              | 96  |

| 9.2. 功能特点 .....              | 96  |

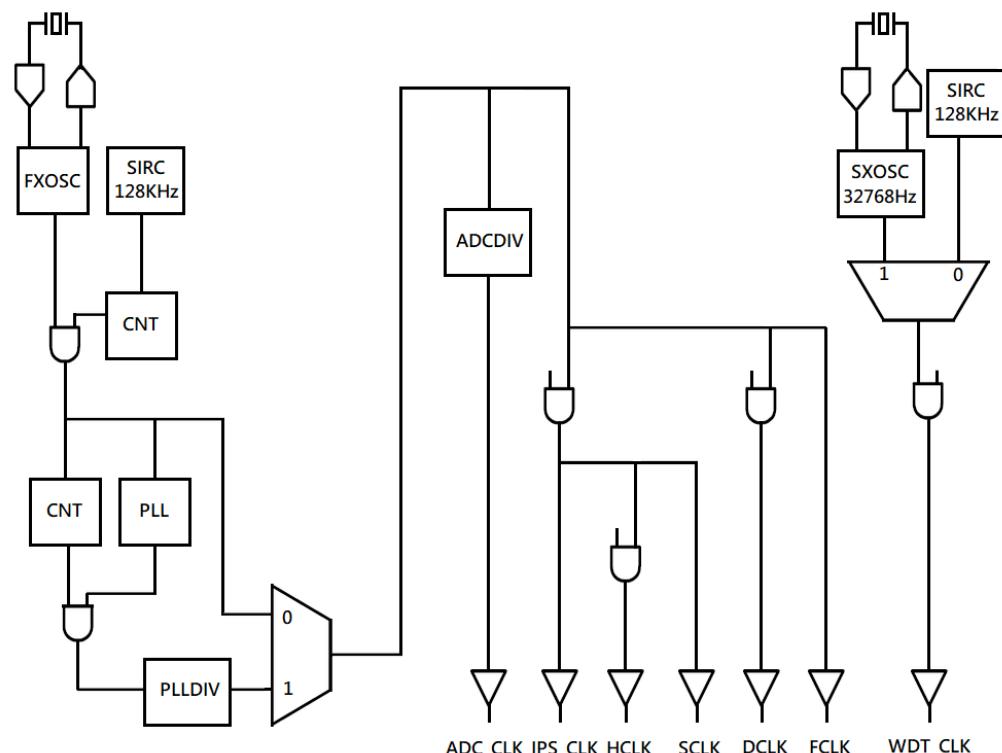

| 9.3. 时钟结构 .....              | 96  |

| 9.4. 时钟源选择 .....             | 97  |

| 9.4.1. 低功耗选项 .....           | 97  |

| 9.5. 内存映射和寄存器 .....          | 97  |

| 9.5.1. 内存映射 .....            | 98  |

| 9.5.2. 寄存器说明 .....           | 99  |

| 9.6. 功能描述 .....              | 115 |

| 9.6.1. 打开 PLL .....          | 115 |

| 9.6.2. PLL 测量的频率 .....       | 115 |

| 9.6.3. 128KHz 测量的频率 .....    | 115 |

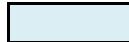

| 10. 复位控制模块 (RCM) .....       | 116 |

| 10.1. 基本概述 .....             | 116 |

| 10.2. 功能特点 .....             | 116 |

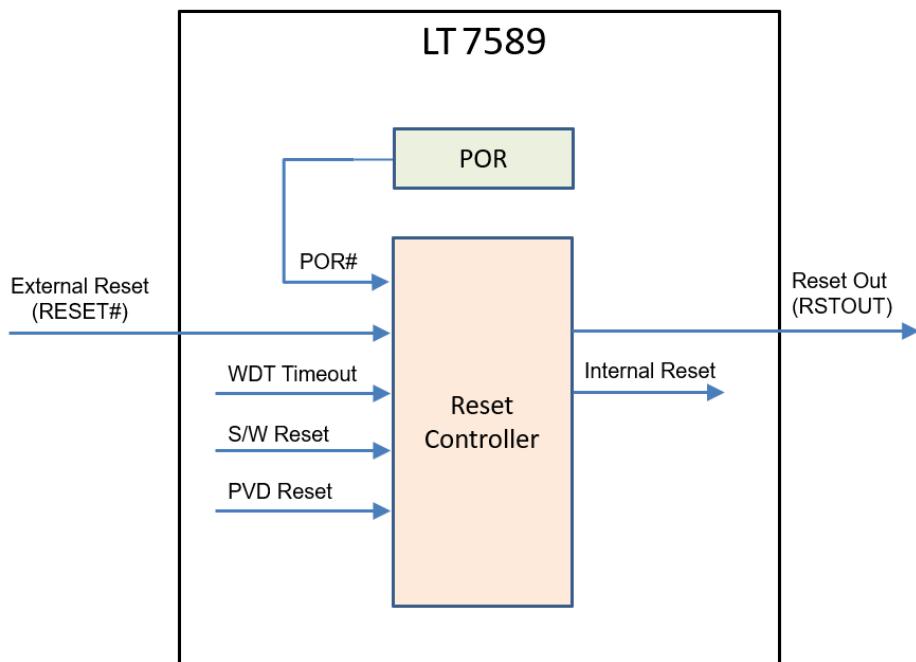

| 10.3. 方块图 .....              | 116 |

| 10.4. 内存映射和寄存器 .....         | 117 |

| 10.4.1. 内存映射 .....           | 117 |

| 10.4.2. 寄存器说明 .....          | 117 |

| 10.5. 功能描述 .....             | 120 |

| 10.5.1. 复位源 .....            | 120 |

| 10.5.2. 复位控制流程 .....         | 120 |

|                                         |     |

|-----------------------------------------|-----|

| 11. 静态随机存取存储器 (SRAM) .....              | 122 |

| 11.1. 功能介绍.....                         | 122 |

| 11.2. 操作模式.....                         | 122 |

| 11.3. 低功耗模式.....                        | 122 |

| 11.4. 复位操作.....                         | 122 |

| 11.5. 中断说明.....                         | 122 |

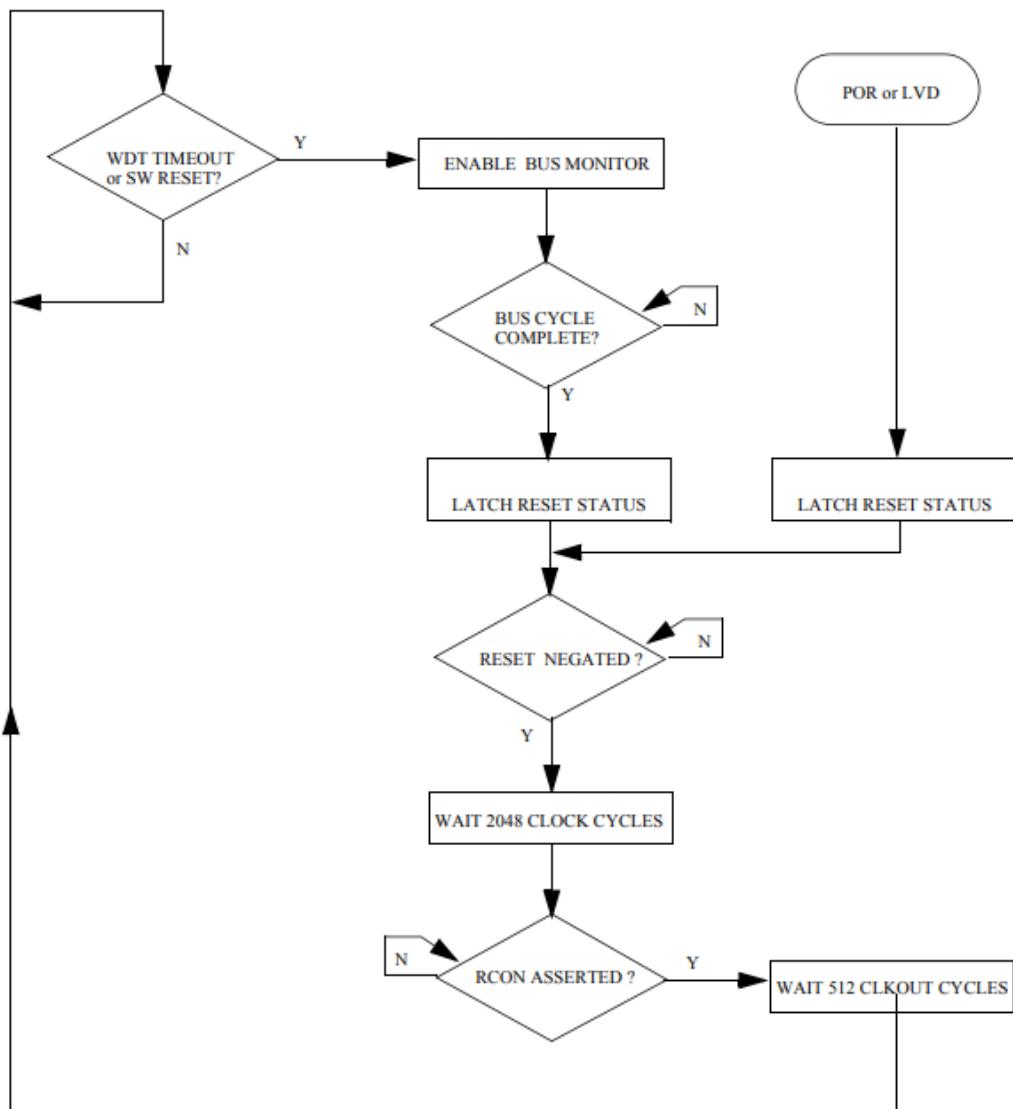

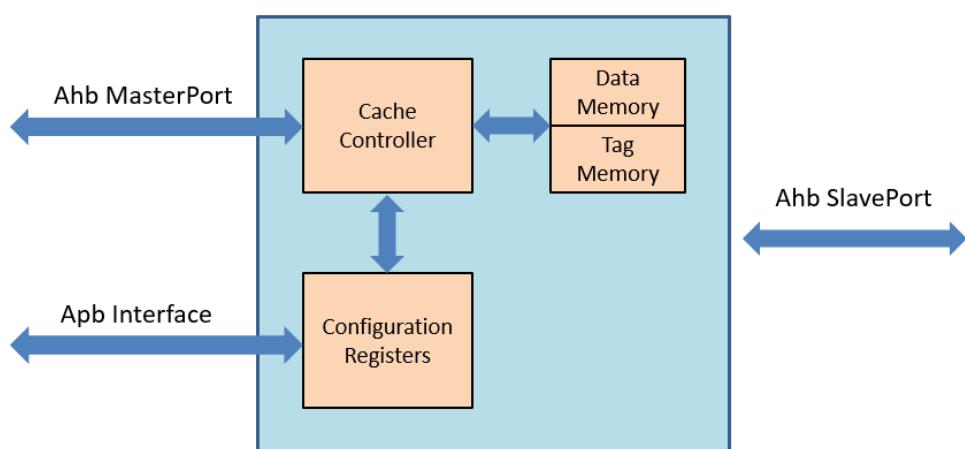

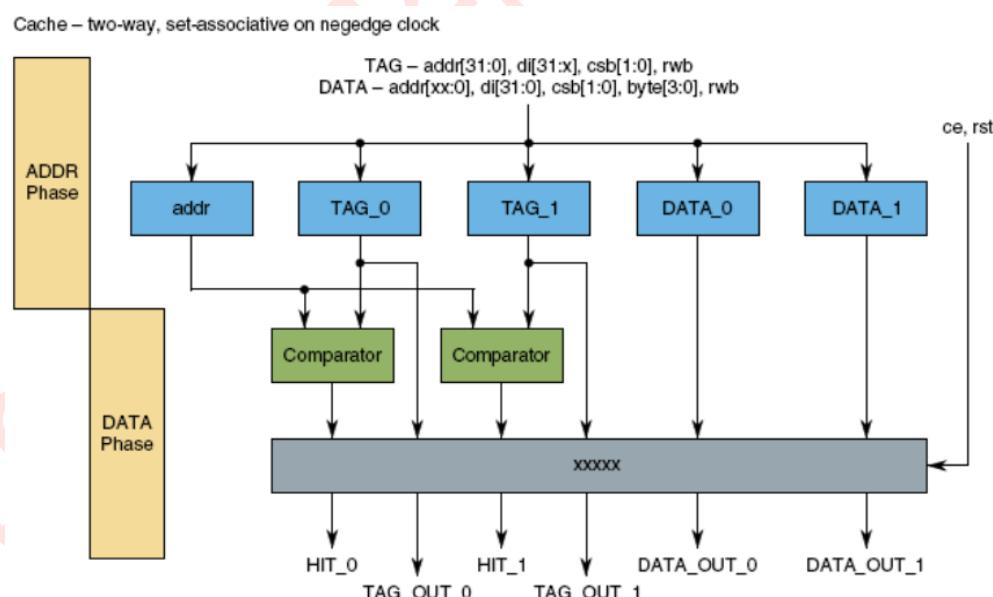

| 12. 高速缓存模块 (CACHEM) .....               | 123 |

| 12.1. 功能介绍.....                         | 123 |

| 12.2. 方块图 .....                         | 124 |

| 12.3. 内存映射和寄存器 .....                    | 125 |

| 12.3.1. 内存映射 .....                      | 125 |

| 12.3.2. 寄存器说明.....                      | 126 |

| 12.4. 缓存功能.....                         | 135 |

| 12.5. Cache 缓存控制 .....                  | 136 |

| 12.5.1. 缓存集命令 .....                     | 136 |

| 12.5.2. Cache Line Commands 缓存行命令 ..... | 137 |

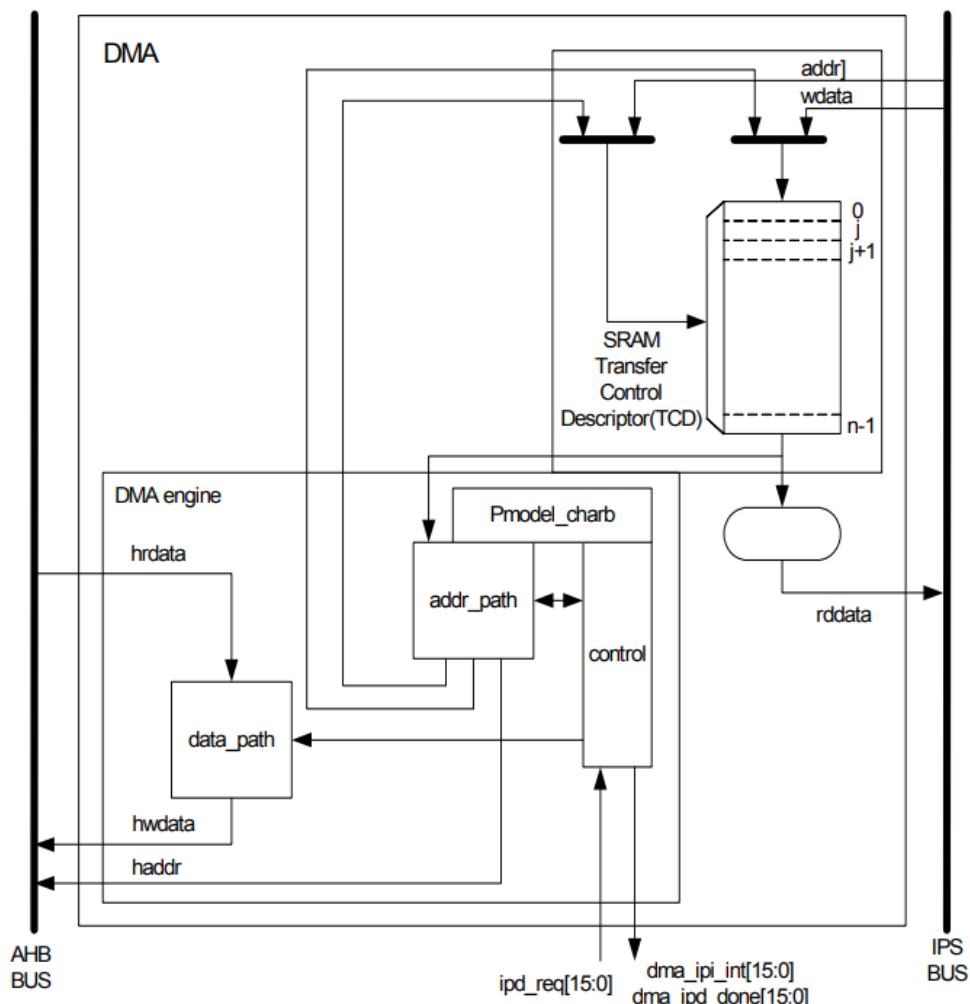

| 13. 直接内存访问控制器 (DMAC) .....              | 140 |

| 13.1. DMA 控制器的具体信息 .....                | 140 |

| 13.1.1. DMAC 功能 .....                   | 140 |

| 13.1.2. 通道分配 .....                      | 141 |

| 13.2. 功能介绍.....                         | 142 |

| 13.2.1. 模块特点 .....                      | 143 |

| 14. 选项字节 (OPB) .....                    | 144 |

| 14.1. 内存映射和寄存器 .....                    | 144 |

| 14.1.1. 内存映射 .....                      | 144 |

| 14.1.2. 寄存器描述.....                      | 144 |

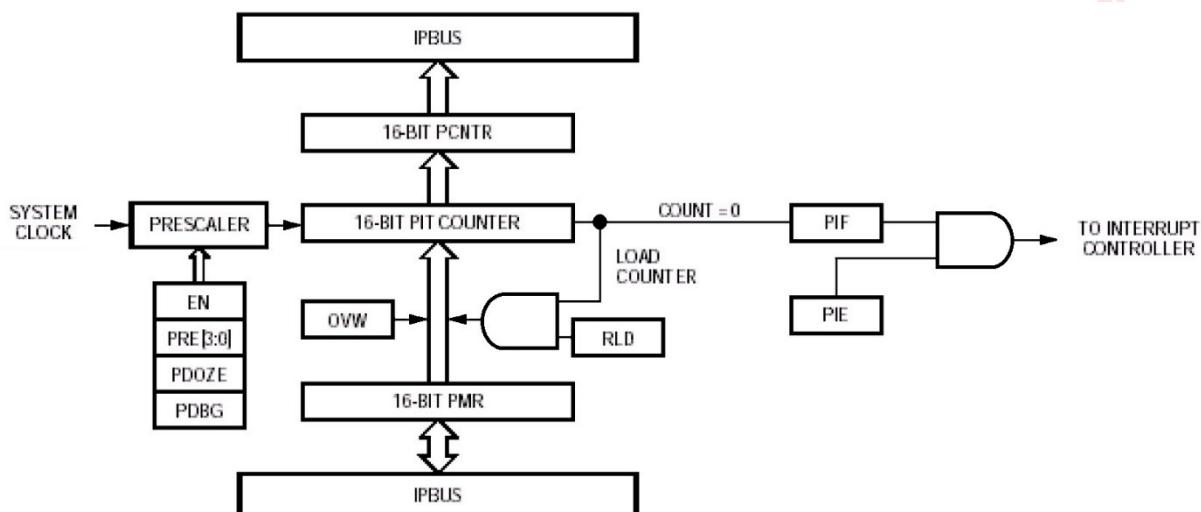

| 15. 编程中断定时器 (PIT) .....                 | 157 |

| 15.1. 功能介绍.....                         | 157 |

| 15.2. 方框方块图 .....                       | 157 |

| 15.3. 操作模式.....                         | 157 |

| 15.3.1. 等待模式 .....                      | 157 |

| 15.3.2. Doze 模式 .....                   | 157 |

| 15.3.3. 停止模式 .....                      | 157 |

|                          |     |

|--------------------------|-----|

| 15.3.4. 调试模块 .....       | 157 |

| 15.4. 信号说明 .....         | 158 |

| 15.5. 内存映射和寄存器 .....     | 158 |

| 15.5.1. 内存映射 .....       | 158 |

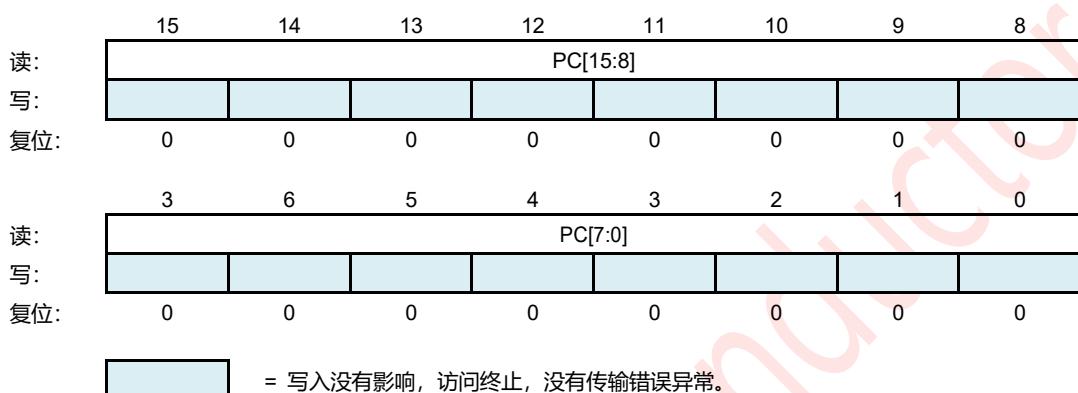

| 15.5.2. 寄存器描述 .....      | 158 |

| 15.6. 功能描述 .....         | 162 |

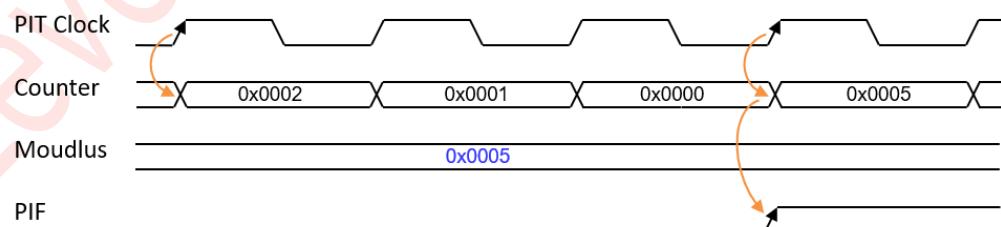

| 15.6.1. 设置和忘记计时器操作 ..... | 162 |

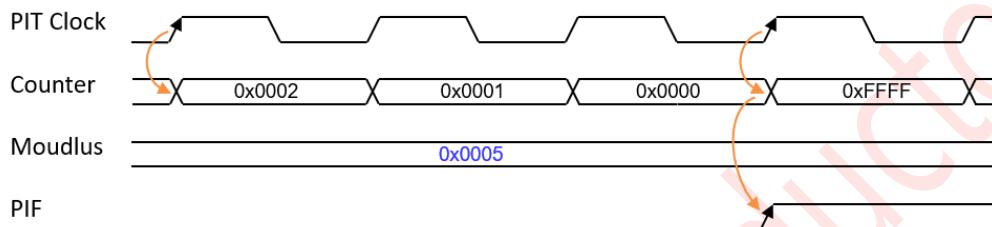

| 15.6.2. 自由运行计时器操作 .....  | 163 |

| 15.6.3. 超时规格 .....       | 163 |

| 15.7. 中断操作 .....         | 163 |

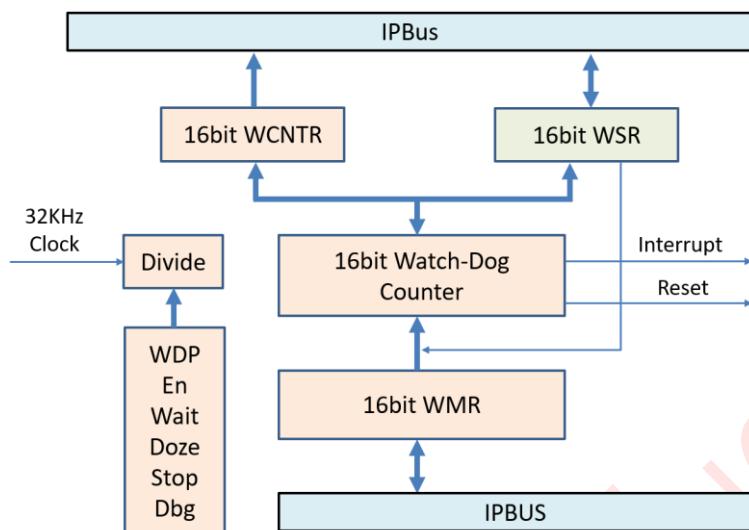

| 16. 看门狗计时器 (WDT) .....   | 164 |

| 16.1. 功能介绍 .....         | 164 |

| 16.2. 操作模式 .....         | 164 |

| 16.2.1. 等待模式 .....       | 164 |

| 16.2.2. Doze 模式 .....    | 164 |

| 16.2.3. 停止模式 .....       | 164 |

| 16.2.4. 调试模式 .....       | 164 |

| 16.3. 方块图 .....          | 165 |

| 16.4. 信号说明 .....         | 165 |

| 16.5. 内存映射和寄存器 .....     | 165 |

| 16.5.1. 内存映射 .....       | 165 |

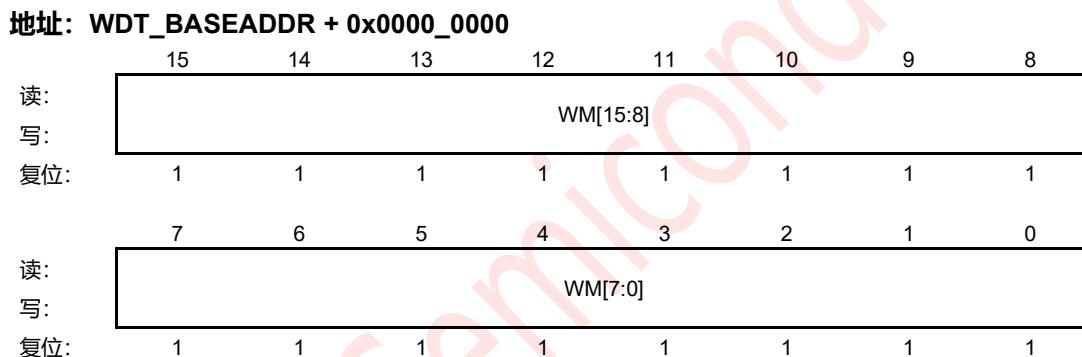

| 16.5.2. 寄存器说明 .....      | 166 |

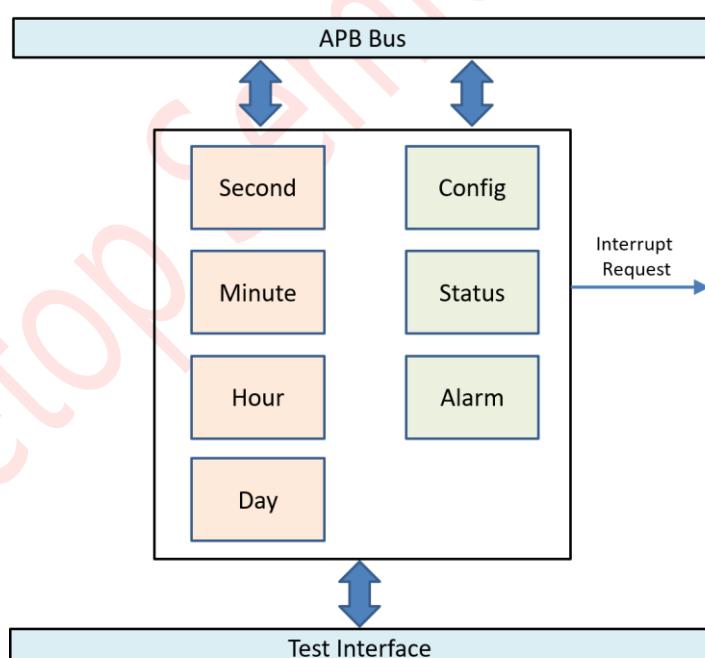

| 17. 时钟控制器 (RTC) .....    | 170 |

| 17.1. 功能介绍 .....         | 170 |

| 17.2. RTC 特点 .....       | 170 |

| 17.3. 测试模式 .....         | 170 |

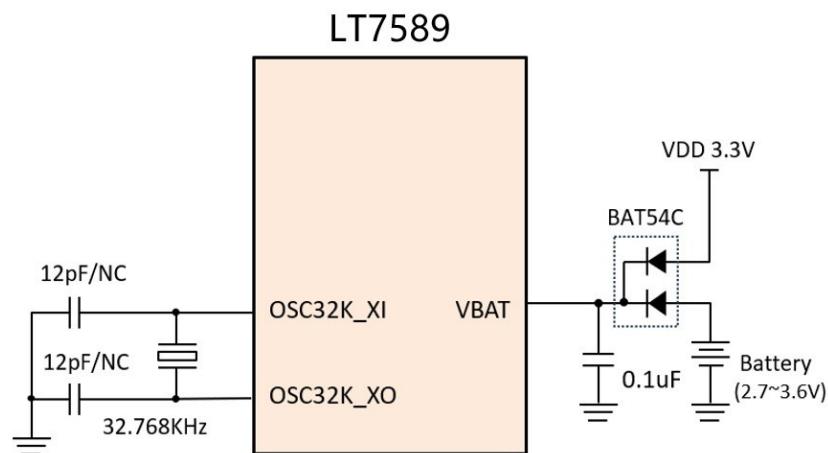

| 17.4. 方块图 .....          | 170 |

| 17.5. 应用电路 .....         | 171 |

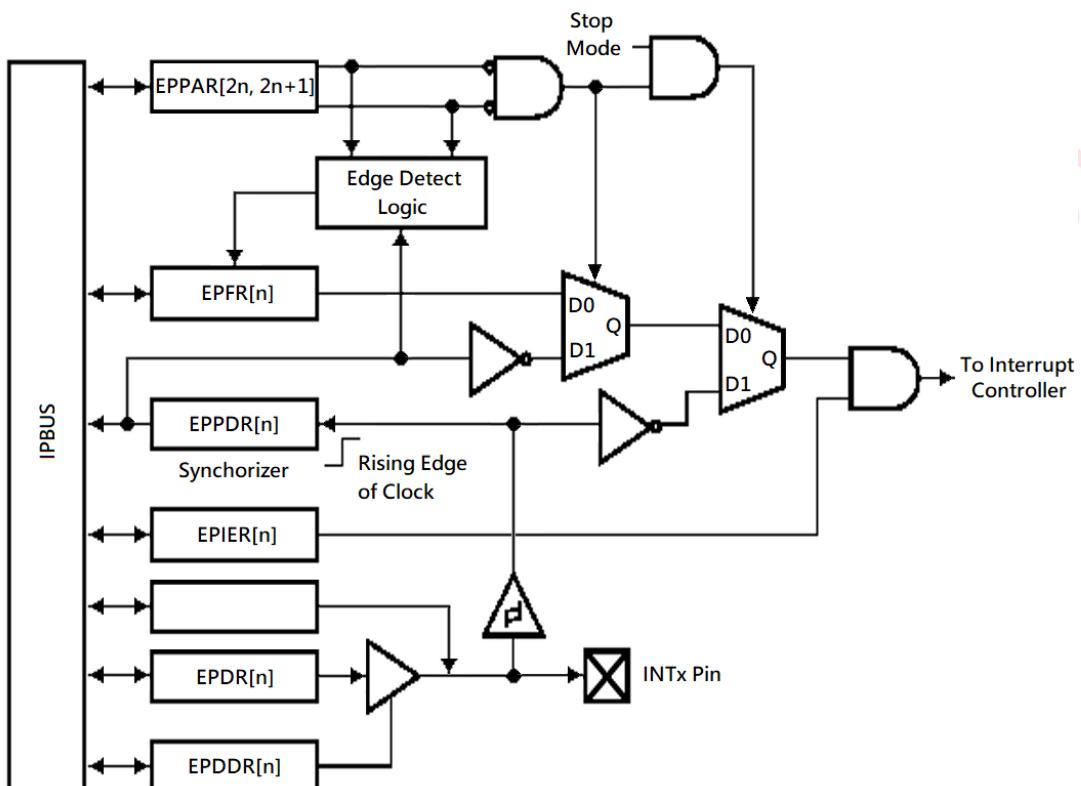

| 18. 边缘端口模块 (EPORT) ..... | 172 |

| 18.1. 功能介绍 .....         | 172 |

| 18.2. 低功耗模式运行 .....      | 172 |

| 18.2.1. 等待和多兹模式 .....    | 172 |

| 18.2.2. 停止模式 .....       | 172 |

| 18.3. 中断/通用输入引脚说明 .....  | 173 |

|                                   |     |

|-----------------------------------|-----|

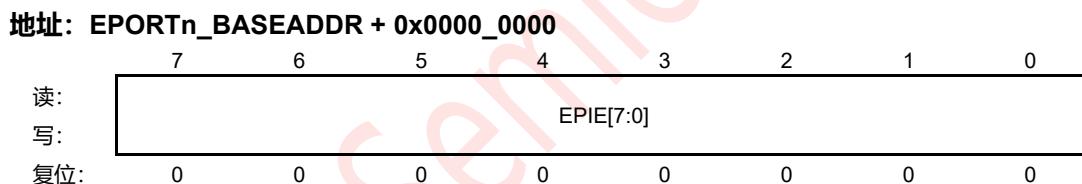

| 18.4. 内存映射和寄存器 .....              | 173 |

| 18.4.1. 内存映射 .....                | 173 |

| 18.4.2. 寄存器说明 .....               | 174 |

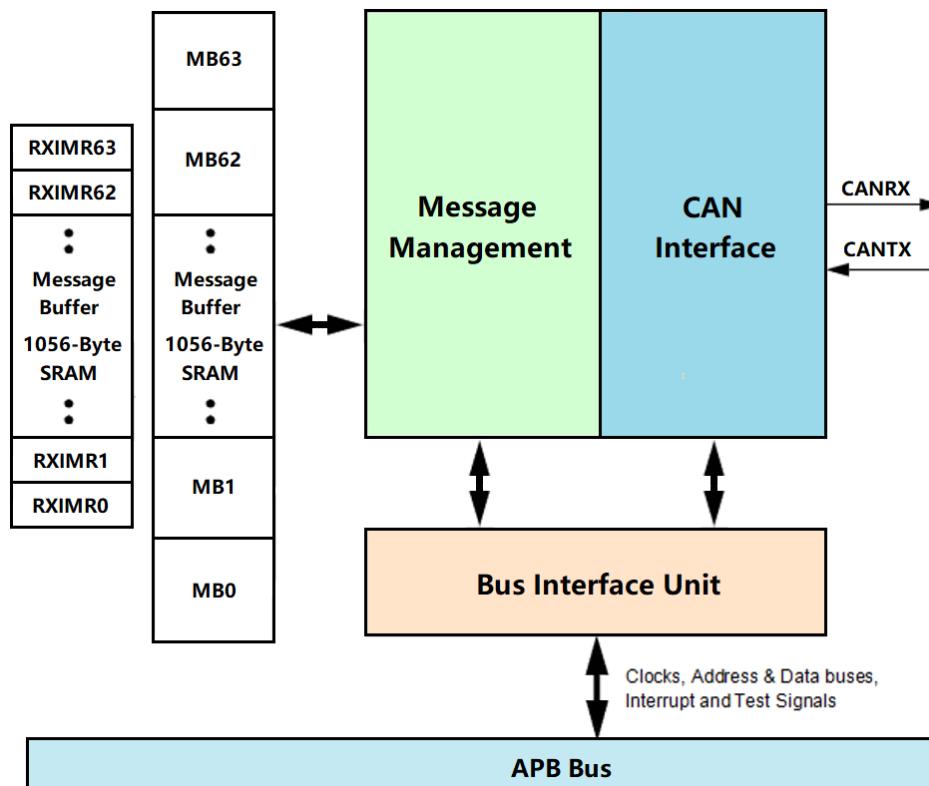

| 19. CANBus 控制程序 (CANBC) .....     | 181 |

| 19.1. 功能介绍 .....                  | 181 |

| 19.1.1. 基本概述 .....                | 181 |

| 19.1.2. CANBus 模块功能 .....         | 182 |

| 19.1.3. 操作模式 .....                | 183 |

| 19.2. 外部信号描述 .....                | 183 |

| 19.2.1. 基本概述 .....                | 183 |

| 19.2.2. 信号描述 .....                | 184 |

| 20. 串行通信接口 (SCI) .....            | 185 |

| 20.1. 功能介绍 .....                  | 185 |

| 20.2. 通信接口特点 .....                | 185 |

| 20.3. 操作模式 .....                  | 186 |

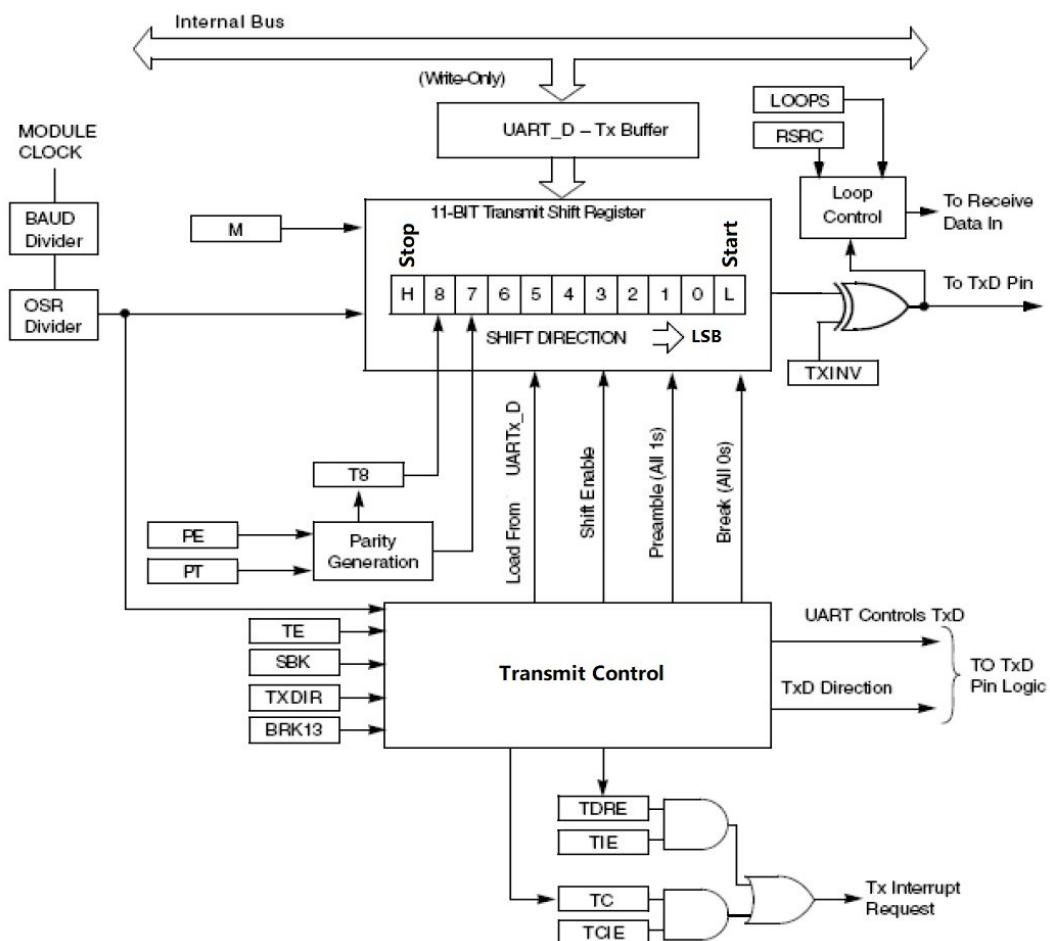

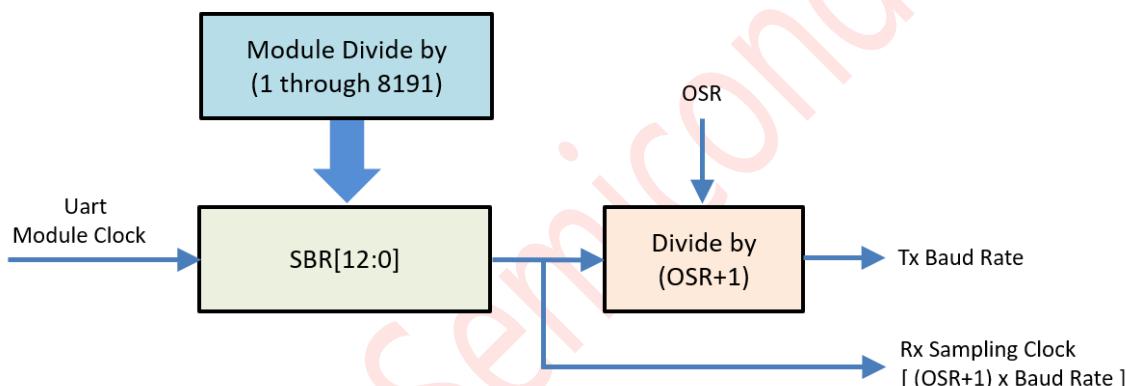

| 20.4. 方块图 .....                   | 186 |

| 20.5. 操作模式 .....                  | 187 |

| 20.5.1. 停止模式 .....                | 187 |

| 20.5.2. 等待 Mode .....             | 187 |

| 20.6. 信号描述 .....                  | 187 |

| 20.7. 内存映射和寄存器 .....              | 188 |

| 20.7.1. 内存映射 .....                | 188 |

| 20.7.2. 寄存器说明 .....               | 189 |

| 20.8. 功能描述 .....                  | 214 |

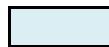

| 20.9. 波特率生成 .....                 | 214 |

| 20.10. 发送器功能描述 .....              | 215 |

| 20.10.1. 发送休息和排队的空闲时间 .....       | 215 |

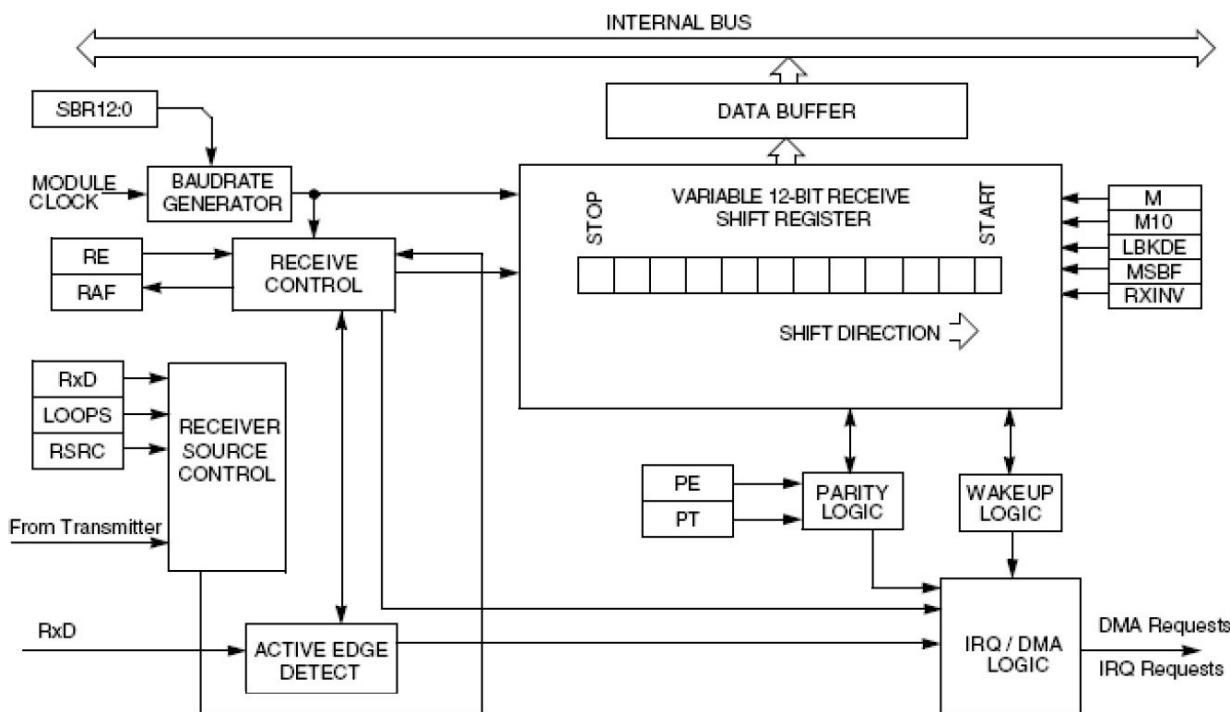

| 20.11. 接收器功能说明 .....              | 216 |

| 20.11.1. 数据采样技术 .....             | 216 |

| 20.11.2. 接收器唤醒操作 .....            | 217 |

| 20.11.3. 红外解码器 .....              | 220 |

| 20.12. 额外的 SCI 功能 .....           | 221 |

| 20.12.1. 8 位、9 位和 10 位的数据模式 ..... | 221 |

| 20.12.2. 空闲长度 .....               | 221 |

| 20.12.3. 单线操作 .....               | 221 |

|                              |     |

|------------------------------|-----|

| 20.12.4. 循环模式 .....          | 222 |

| 20.13. 红外线接口 .....           | 222 |

| 20.13.1. 红外发射编码器 .....       | 222 |

| 20.13.2. 红外接收解码器 .....       | 222 |

| 20.14. 中断和状态标志 .....         | 223 |

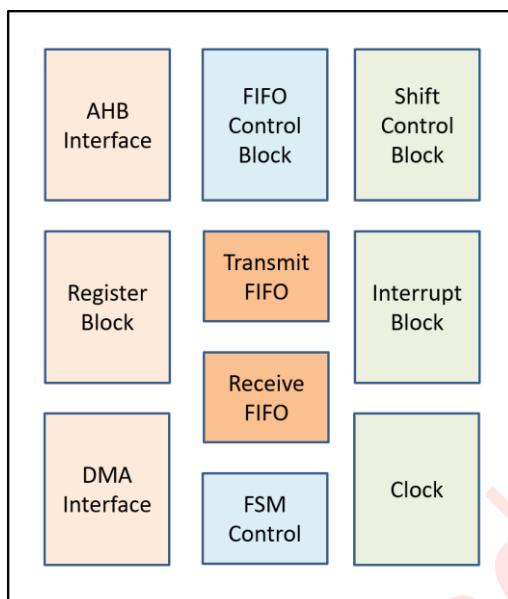

| 21. 同步串行接口 (SSI) .....       | 224 |

| 21.1. 功能介绍 .....             | 224 |

| 21.2. 串行接口特点 .....           | 224 |

| 21.3. 操作模式 .....             | 224 |

| 21.4. 方块图 .....              | 225 |

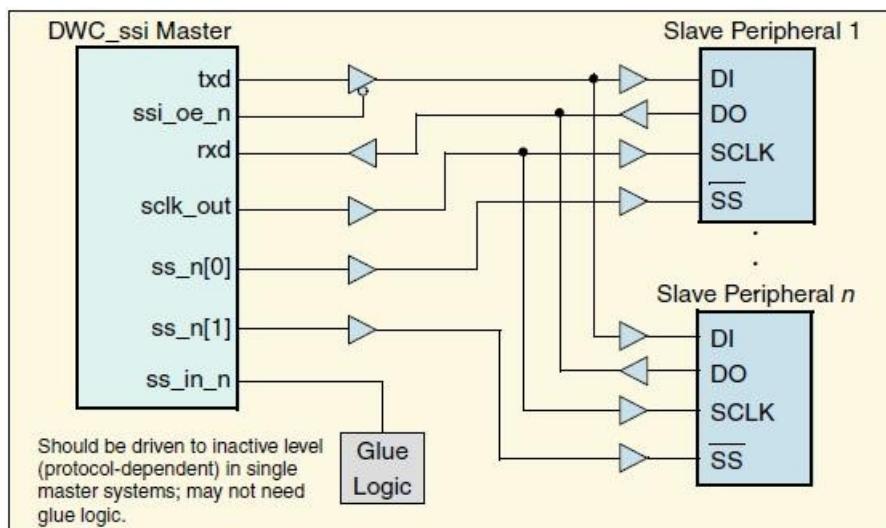

| 21.5. 应用图 .....              | 225 |

| 21.6. 内存映射和寄存器 .....         | 226 |

| 21.6.1. 内存映射 .....           | 226 |

| 21.6.2. 寄存器描述 .....          | 227 |

| 21.7. 功能描述 .....             | 265 |

| 21.7.1. 主模式 .....            | 265 |

| 21.7.2. 时钟比率 .....           | 265 |

| 21.7.3. 接收和传输 FIFO 缓冲区 ..... | 266 |

| 21.7.4. DMA 操作 .....         | 266 |

| 21.7.5. SSI 中断 .....         | 266 |

| 21.7.6. 增强的 SPI 模式 .....     | 267 |

| 21.7.7. 就地执行 (XIP) 模式 .....  | 268 |

| 21.7.8. 在 XIP 中的连续传输模式 ..... | 268 |

| 21.7.9. 在 XIP 操作中的数据预取 ..... | 269 |

| 22. 脉冲宽度调制器 (PWM) .....      | 270 |

| 22.1. 功能介绍 .....             | 270 |

| 22.2. PWM 特点 .....           | 270 |

| 22.3. 方块图 .....              | 271 |

| 22.4. 信号描述 .....             | 271 |

| 22.5. 内存映射和寄存器 .....         | 272 |

| 22.5.1. 内存映射 .....           | 272 |

| 22.5.2. 寄存器描述 .....          | 273 |

| 22.6. 功能描述 .....             | 295 |

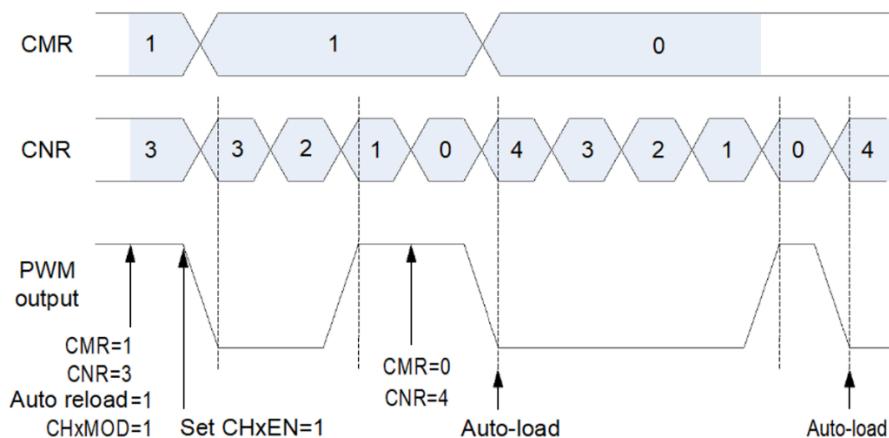

| 22.6.1. PWM 双缓冲和自动重新加载 ..... | 295 |

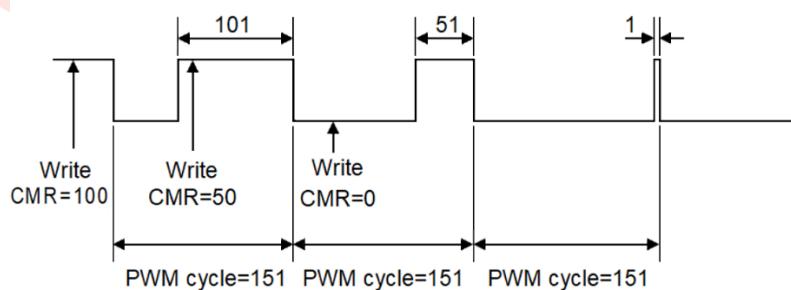

| 22.6.2. 调节占空比 .....          | 295 |

|                                       |            |

|---------------------------------------|------------|

| 22.6.3. 死区发电机.....                    | 296        |

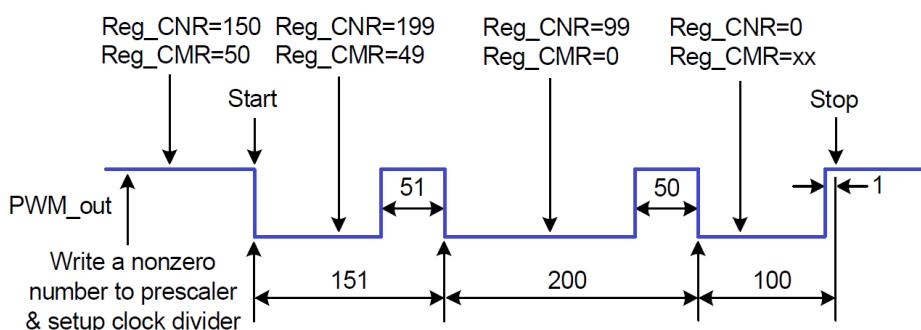

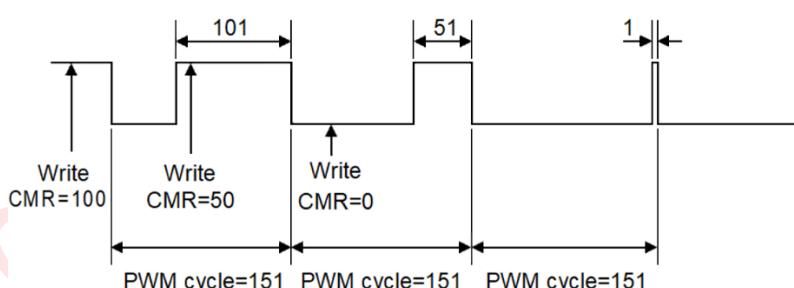

| 22.6.4. PWM 计时器启动过程.....              | 296        |

| 22.6.5. PWM 计时器停止程序.....              | 296        |

| 22.6.6. 捕获启动过程.....                   | 297        |

| 22.6.7. 捕获基本计时器操作 .....               | 297        |

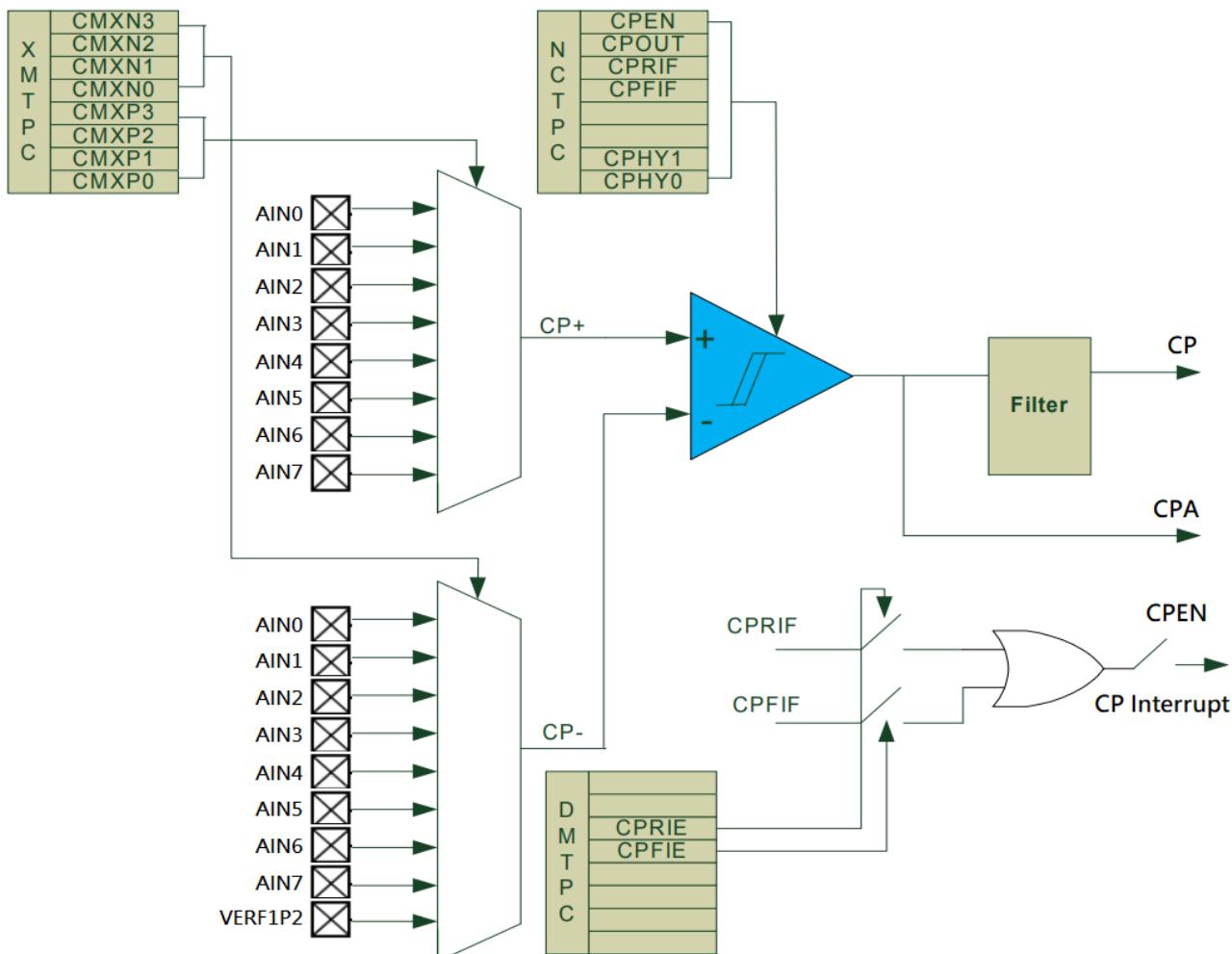

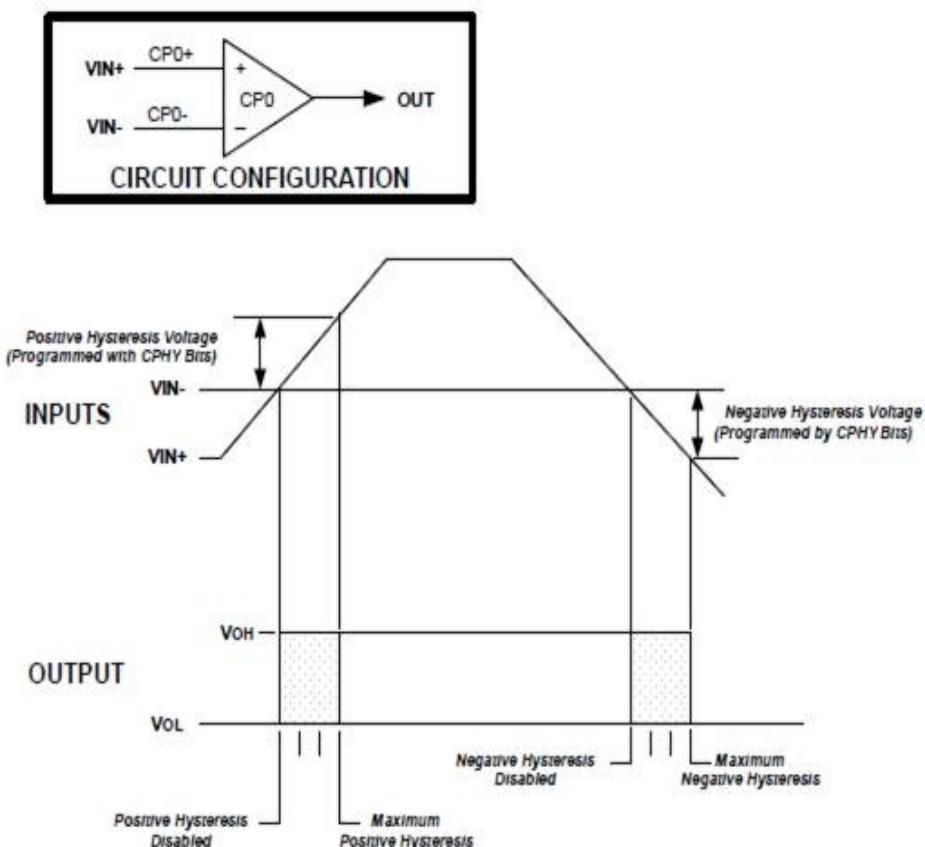

| <b>23. 模拟比较器 (COMP) .....</b>         | <b>298</b> |

| 23.1. 功能介绍.....                       | 298        |

| 23.2. 方块图 .....                       | 298        |

| 23.3. 操作模式.....                       | 299        |

| 23.3.1. 等待模式 .....                    | 299        |

| 23.3.2. Doze 模式 .....                 | 299        |

| 23.3.3. 停止模式 .....                    | 299        |

| 23.4. 内存映射和寄存器 .....                  | 299        |

| 23.4.1. 内存映射 .....                    | 299        |

| 23.4.2. 寄存器描述.....                    | 300        |

| 23.5. 功能描述.....                       | 303        |

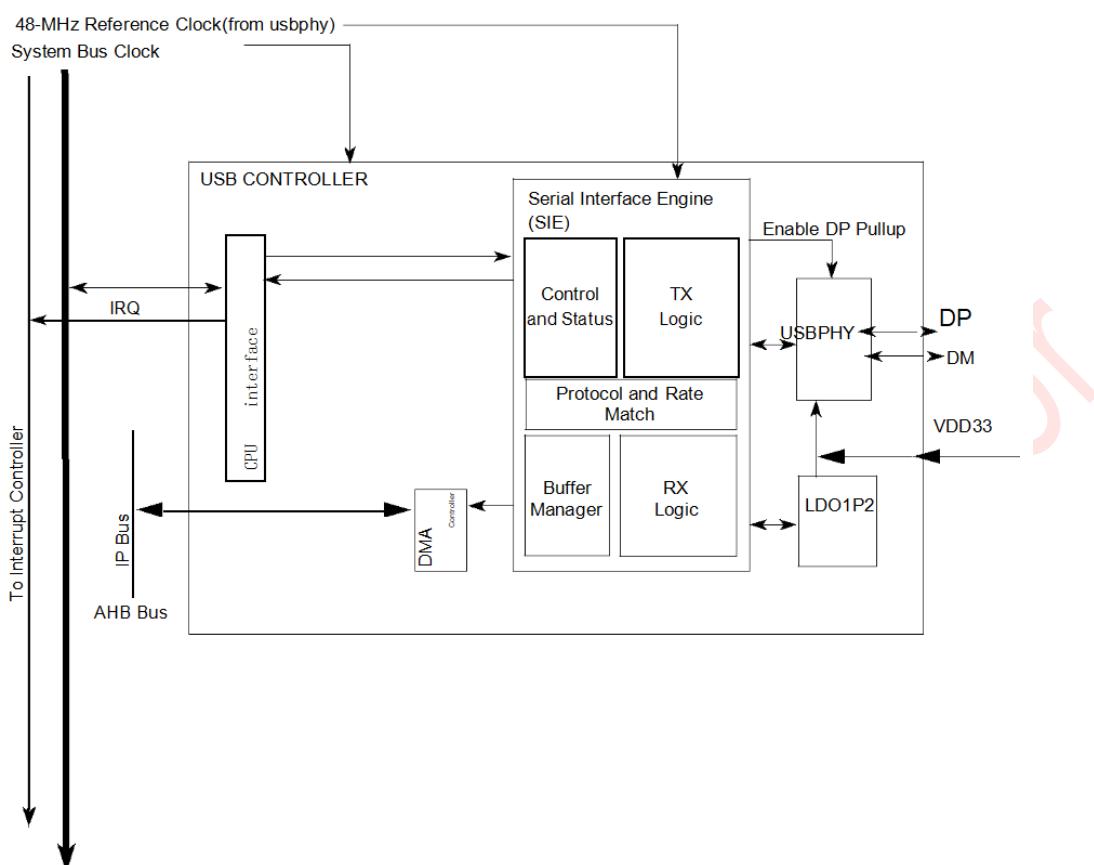

| <b>24. USB2.0 控制器 (USBC) .....</b>    | <b>305</b> |

| 24.1. 功能介绍.....                       | 305        |

| 24.2. USB 模块特点 .....                  | 305        |

| 24.3. 方块图 .....                       | 306        |

| 24.4. 操作模式.....                       | 306        |

| 24.4.1. 等待模式 .....                    | 306        |

| 24.4.2. Doze 模式 .....                 | 306        |

| 24.4.3. 停止模式 .....                    | 306        |

| 24.5. 内存映射和寄存器 .....                  | 307        |

| 24.5.1. 内存映射 .....                    | 307        |

| 24.5.2. 寄存器描述.....                    | 308        |

| 24.6. 功能描述.....                       | 333        |

| 24.6.1. 数据结构 .....                    | 333        |

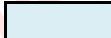

| 24.6.2. 端点缓冲区表 .....                  | 333        |

| 24.6.3. Rx vs. Tx 作为一个 USB 目标设备 ..... | 334        |

| 24.6.4. 寻址端点缓冲区表条目 .....              | 334        |

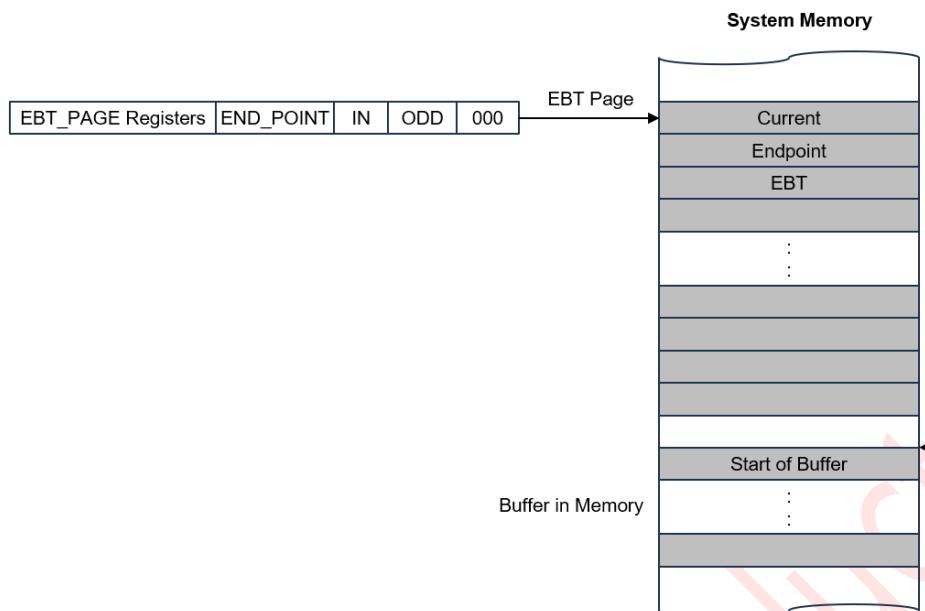

| 24.6.5. 端点缓冲区表格式 .....                | 335        |

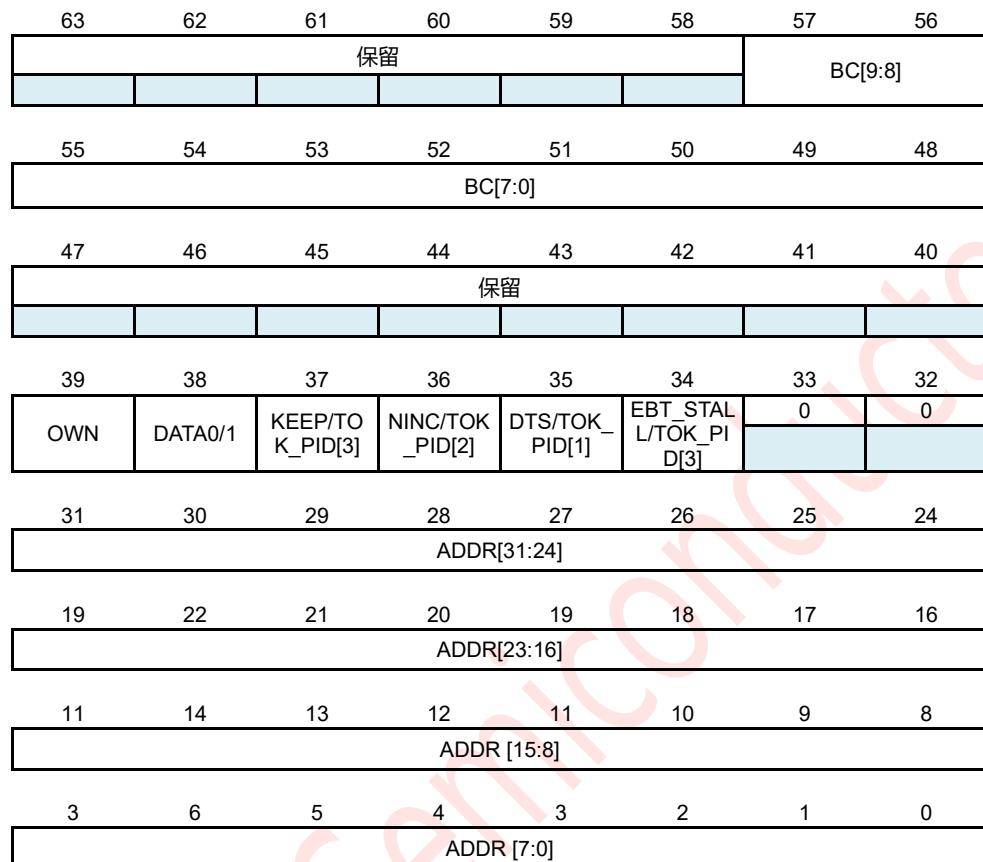

| 24.6.6. USB Transaction.....          | 338        |

| <b>25. 模数转换器 (ADC) .....</b>          | <b>340</b> |

|                                            |     |

|--------------------------------------------|-----|

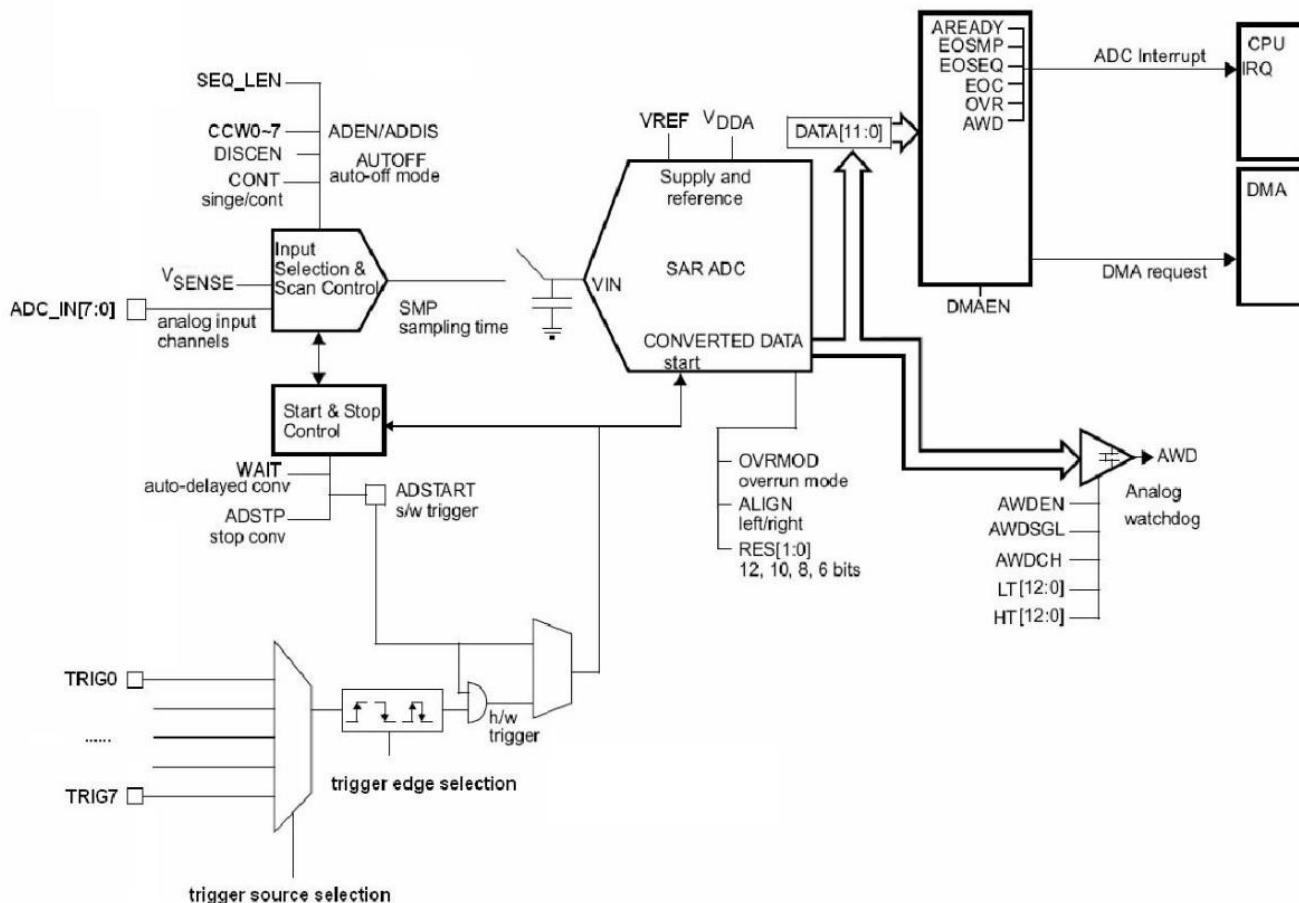

| 25.1. 功能介绍.....                            | 340 |

| 25.2. ADC 主要功能 .....                       | 340 |

| 25.3. ADC 功能描述 .....                       | 341 |

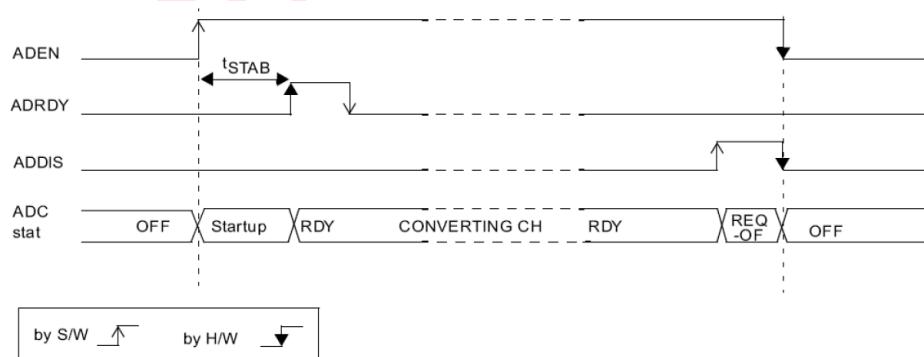

| 25.3.1. ADC 开关控制 (ADEN、ADDIS、ADRDY) .....  | 342 |

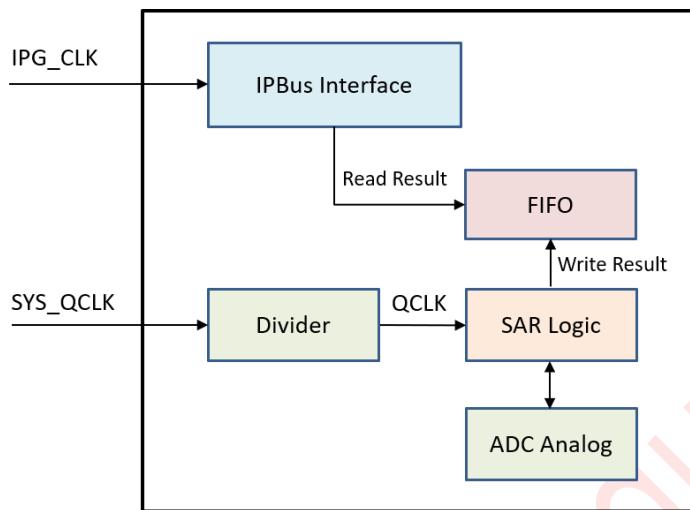

| 25.3.2. ADC 时钟 .....                       | 343 |

| 25.3.3. 配置 ADC .....                       | 343 |

| 25.3.4. 通道选择 (CCWi) .....                  | 343 |

| 25.3.5. 可编程采样时间 (SMP) .....                | 344 |

| 25.3.6. 单次转换模式 (CONT = 0) .....            | 344 |

| 25.3.7. 连续转换模式 (CONT = 1) .....            | 345 |

| 25.3.8. 正在启动转换 (ADSTART) .....             | 345 |

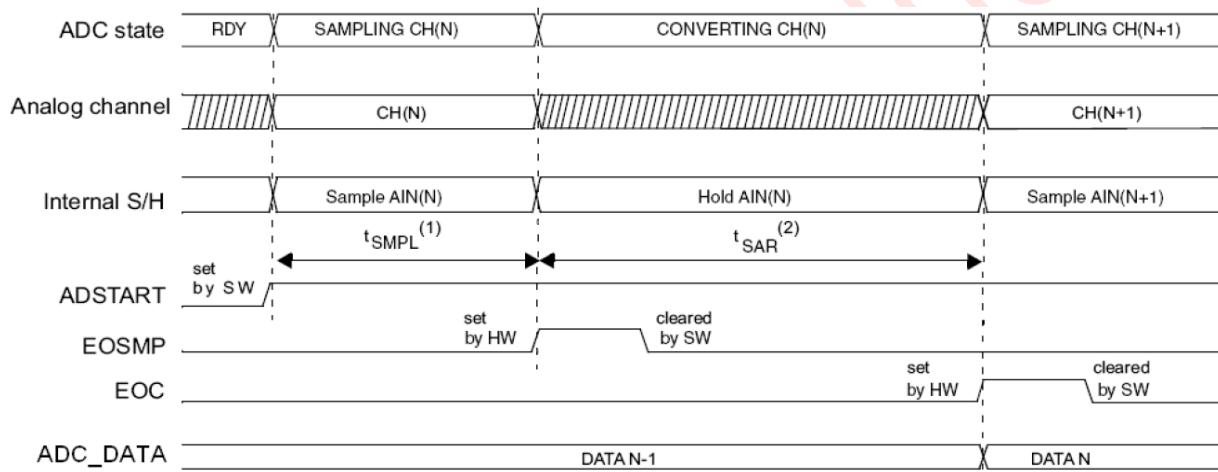

| 25.3.9. 时间安排 .....                         | 346 |

| 25.3.10. 停止一个持续的转换 (ADSTP) .....           | 347 |

| 25.4. 在外部触发器和触发器极性上的转换.....                | 347 |

| 25.4.1. 不连续模式 (DISCEN) .....               | 349 |

| 25.4.2. 可编程分辨率 (RES) - 快速转换模式.....         | 349 |

| 25.4.3. 转换结束, 采样阶段结束(EOC、EOSMP Flag) ..... | 350 |

| 25.4.4. 转换序列的结束(Eoseq Flag) .....          | 350 |

| 25.4.5. 时序图范例.....                         | 350 |

| 25.5. 数据管理.....                            | 352 |

| 25.5.1. 数据 FIFO 和数据对齐(ADC_FIFO, 对齐) .....  | 352 |

| 25.5.2. ADC 超运行 (OVR、OVRMOD) .....         | 352 |

| 25.5.3. 管理不使用 DMA 而转换的数据序列.....            | 353 |

| 25.5.4. 管理转换的数据而不使用 DMA.....               | 353 |

| 25.5.5. 使用 DMA 管理转换后的数据.....               | 353 |

| 25.6. 低功耗功能 .....                          | 354 |

| 25.6.1. 等待模式转换 .....                       | 354 |

| 25.6.2. 自动关闭模式 (AUTOFF) .....              | 354 |

| 25.7. 模拟窗口看门狗 (AWD) .....                  | 354 |

| 25.8. 温度传感器 .....                          | 355 |

| 25.9. ADC 中断 .....                         | 355 |

| 25.10. 内存映射和寄存器 .....                      | 356 |

| 25.10.1. 内存映射 .....                        | 356 |

| 25.10.2. 寄存器描述.....                        | 357 |

| 26. TFT LCD 控制器的寄存器.....                   | 370 |

| 26.1. PWM 控制寄存器 .....                      | 370 |

|                                   |            |

|-----------------------------------|------------|

| 26.2. GPIO 寄存器 .....              | 373        |

| <b>27. 电气特性 .....</b>             | <b>375</b> |

| 27.1. 极限参数 .....                  | 375        |

| 27.2. DC 电气参数 .....               | 375        |

| 27.3. ESD 保护规格 .....              | 377        |

| <b>28. 封装信息 .....</b>             | <b>378</b> |

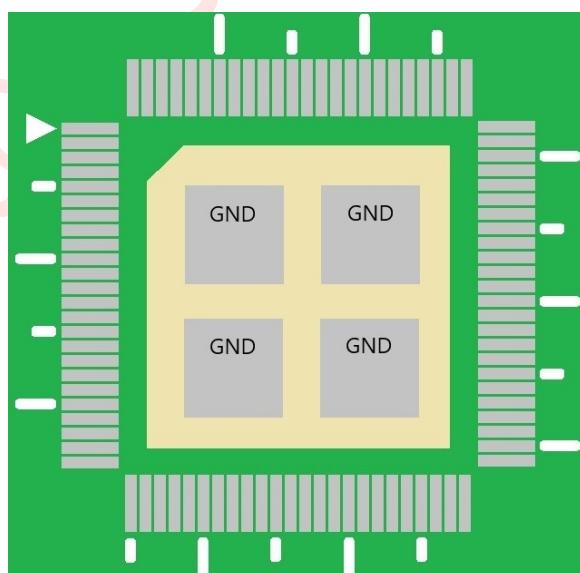

| 28.1. LT7589A (QFN-96pin) .....   | 378        |

| 28.2. LT7589B (LQFP-128pin) ..... | 379        |

| 28.3. LT7589A PCB 板布局建议 .....     | 380        |

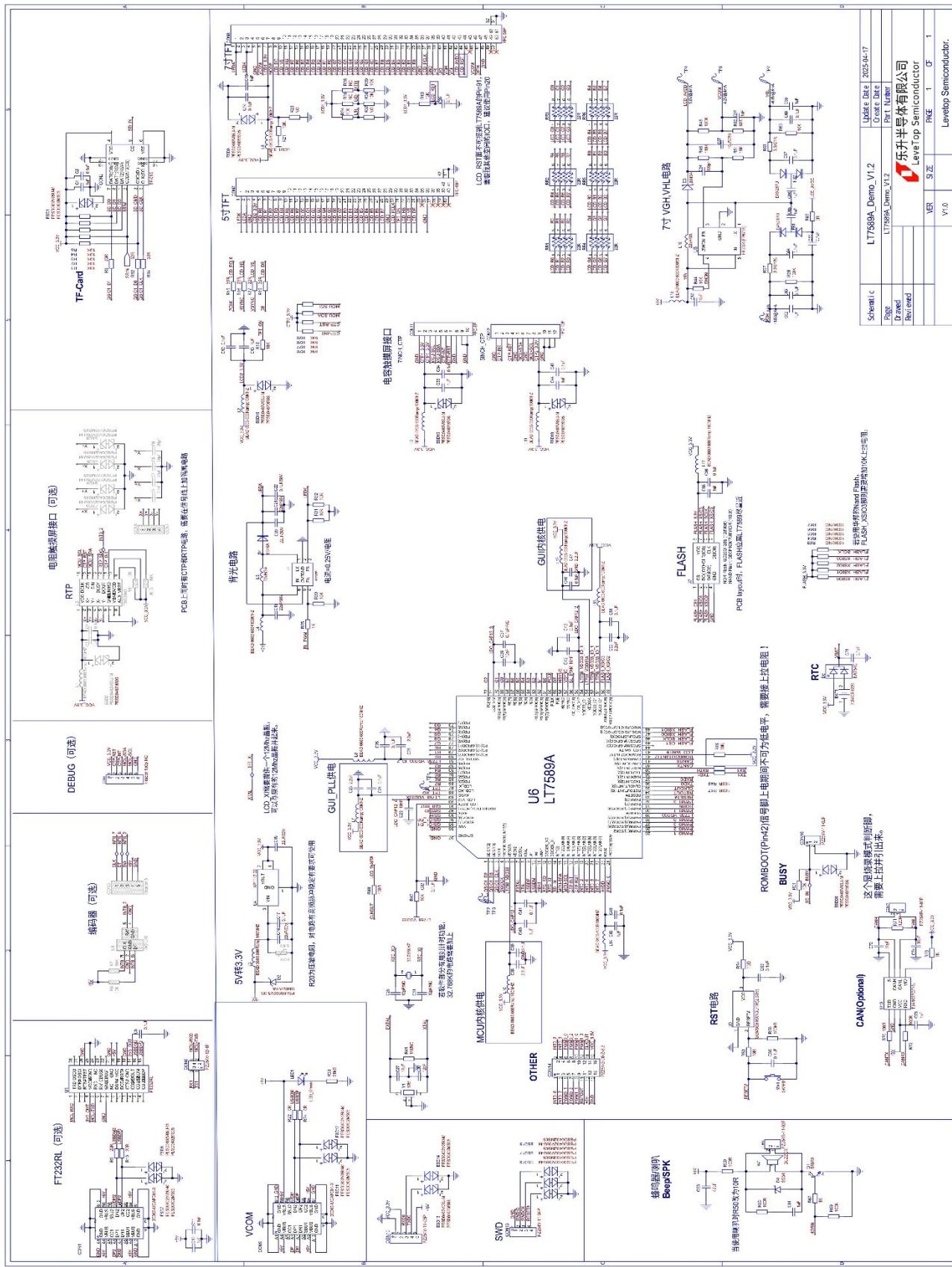

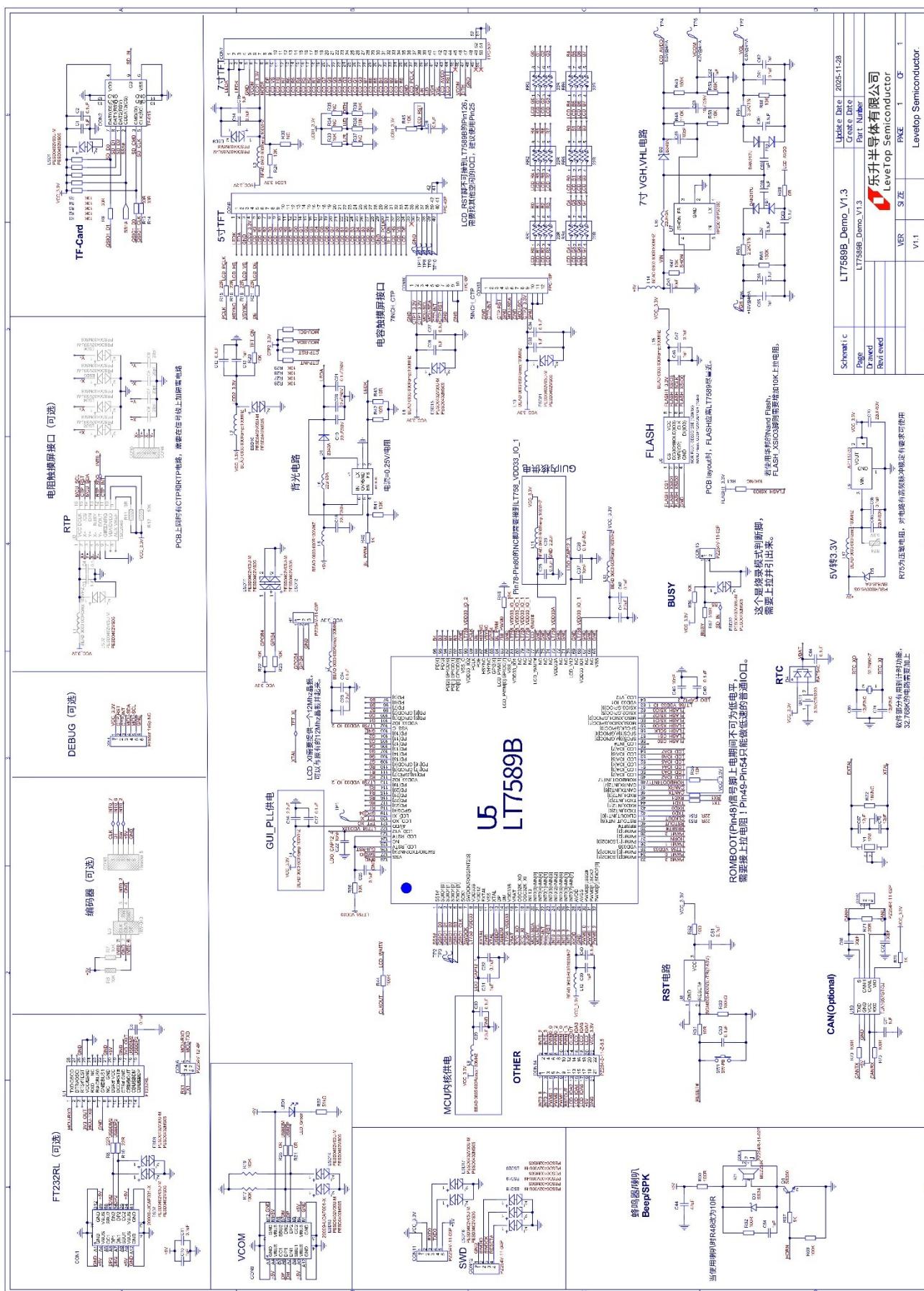

| <b>29. 原理图 .....</b>              | <b>381</b> |

## 图 列 表

|                                                 |    |

|-------------------------------------------------|----|

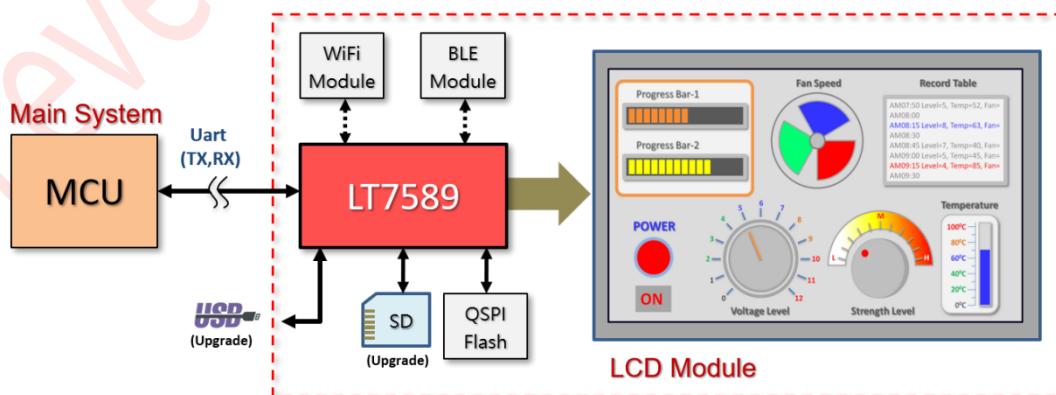

| 图 1-1: LT7589 设置在模块板上 .....                     | 23 |

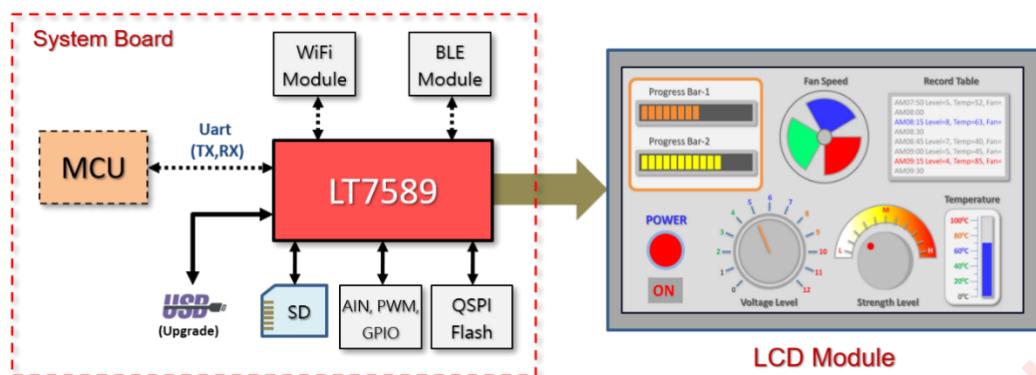

| 图 1-2: LT7589 设置在系统主板上 .....                    | 24 |

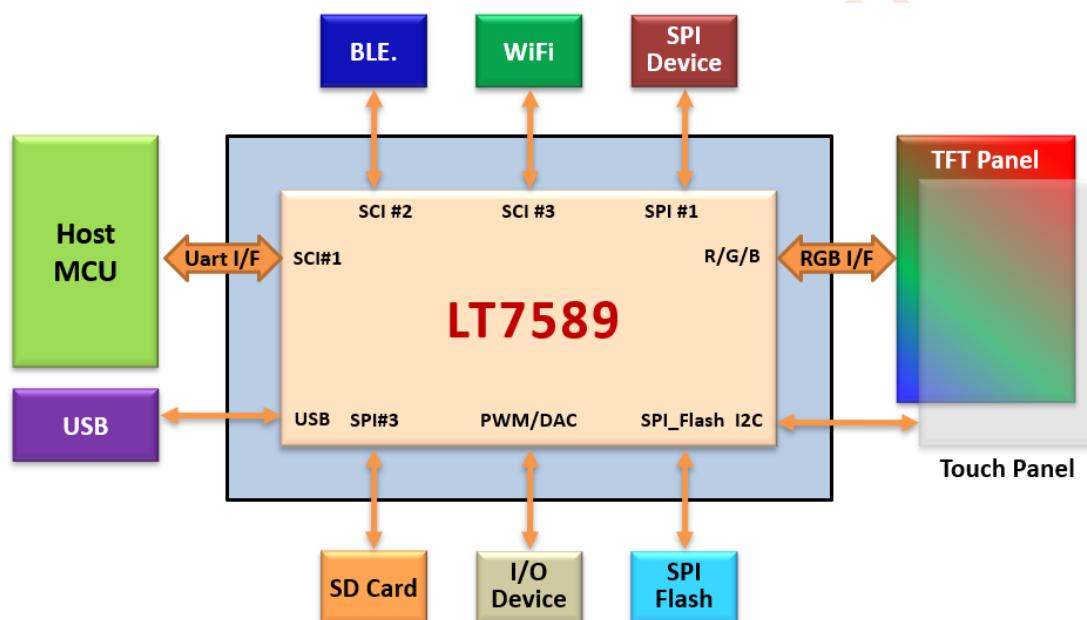

| 图 1-3: LT7589 应用架构 .....                        | 24 |

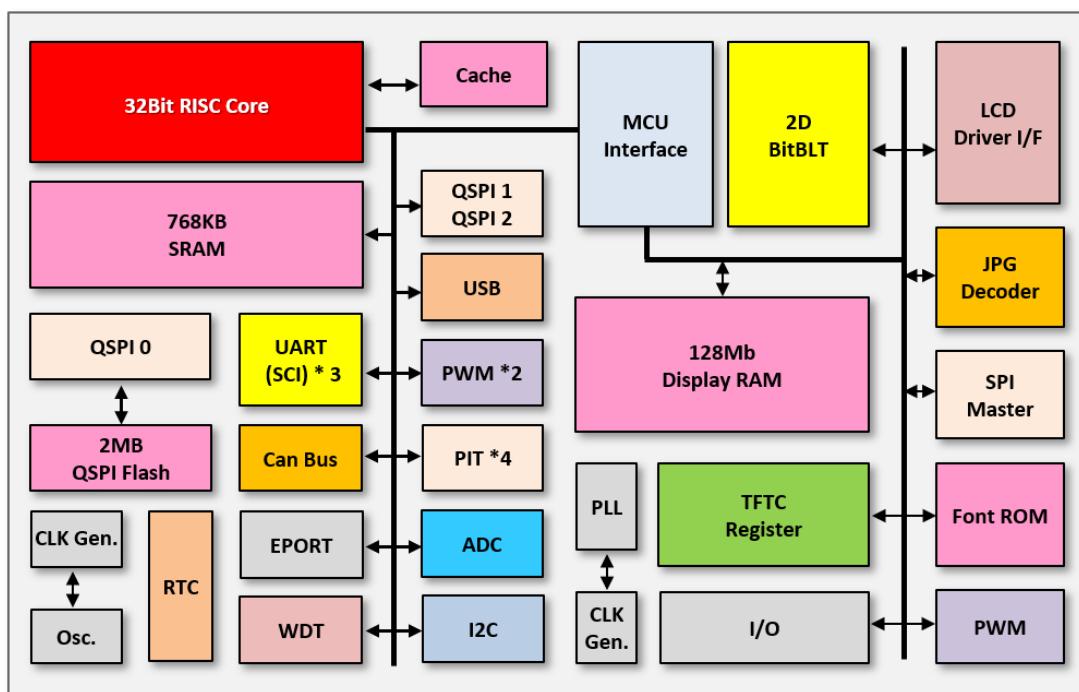

| 图 1-4: LT7589 内部方块图 .....                       | 25 |

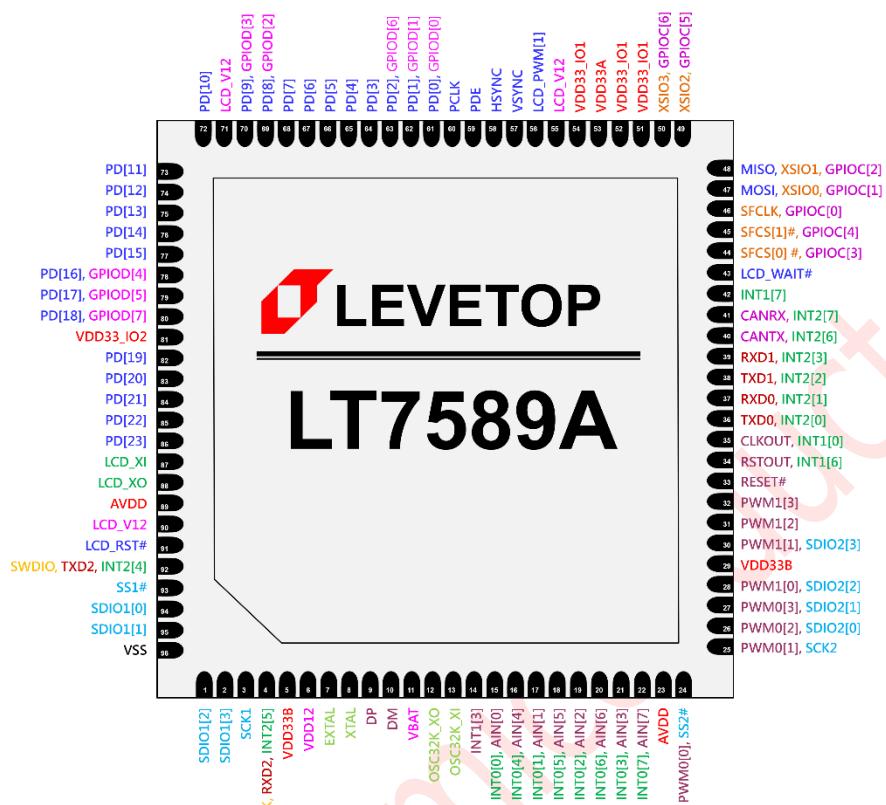

| 图 2-1: LT7589A 引脚图 (QFN-96Pin) .....            | 28 |

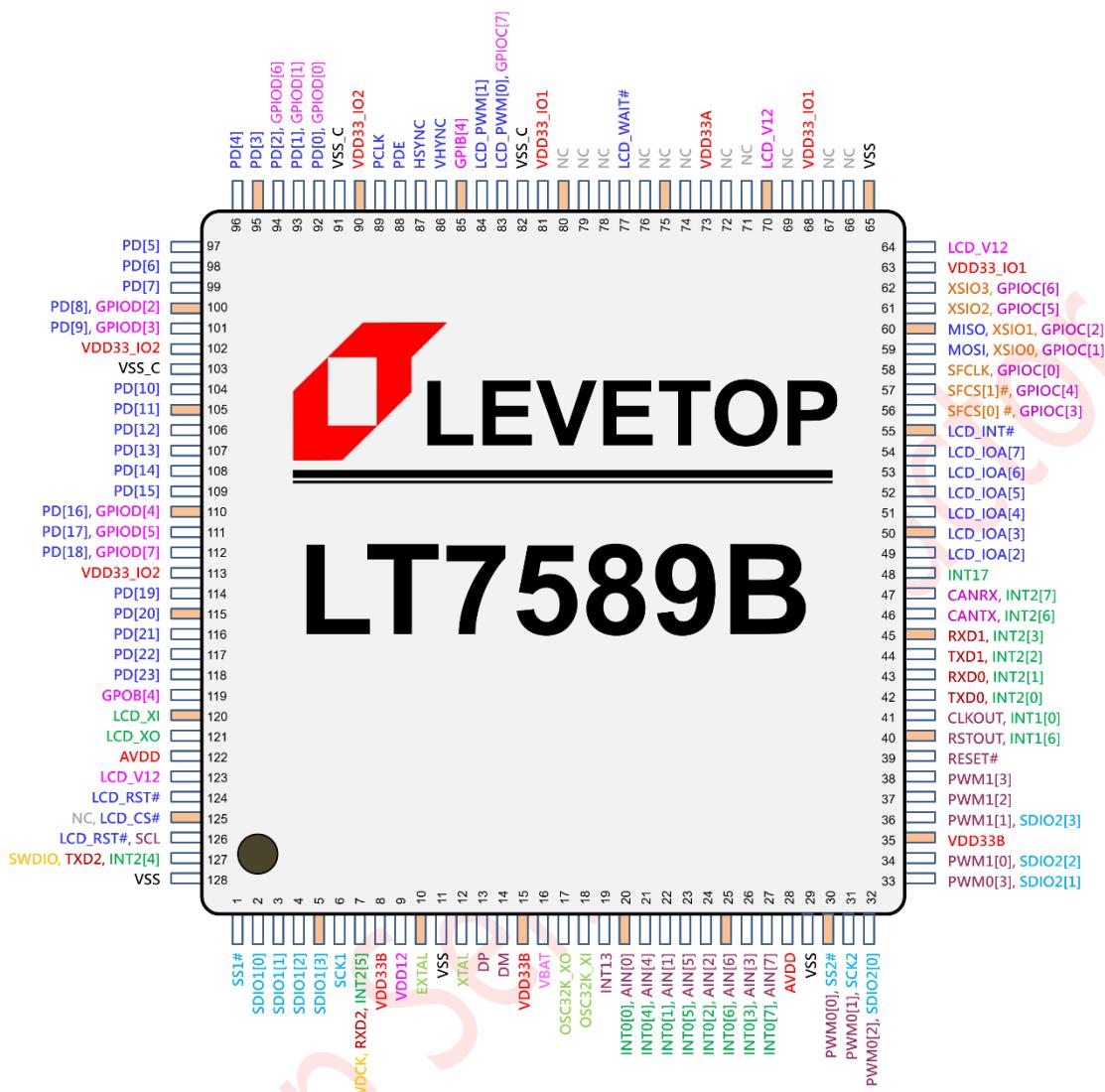

| 图 2-2: LT7589B 引脚图 (LQFP-128Pin) .....          | 29 |

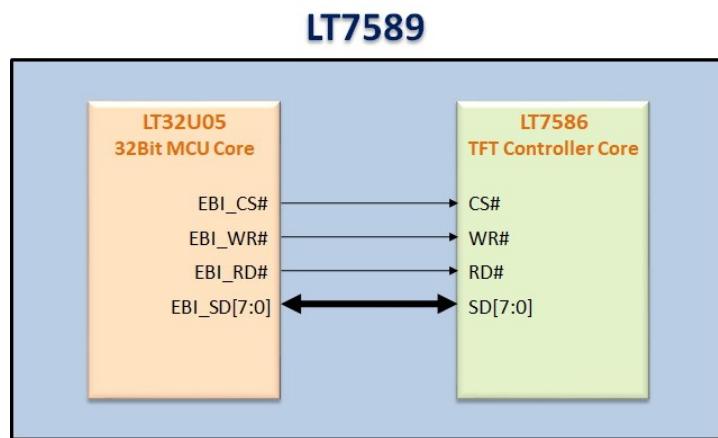

| 图 3-1: LT7589 内部 MCU 与 TFT 图形加速器的连接图 .....      | 43 |

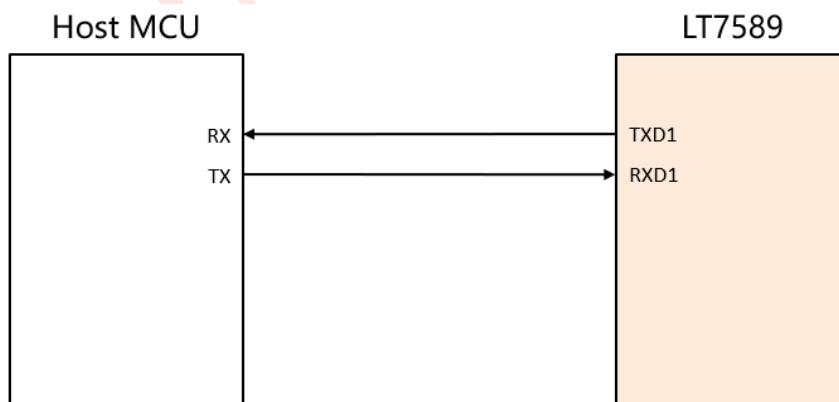

| 图 3-2: 与主控端 MCU 的通信模式 .....                     | 43 |

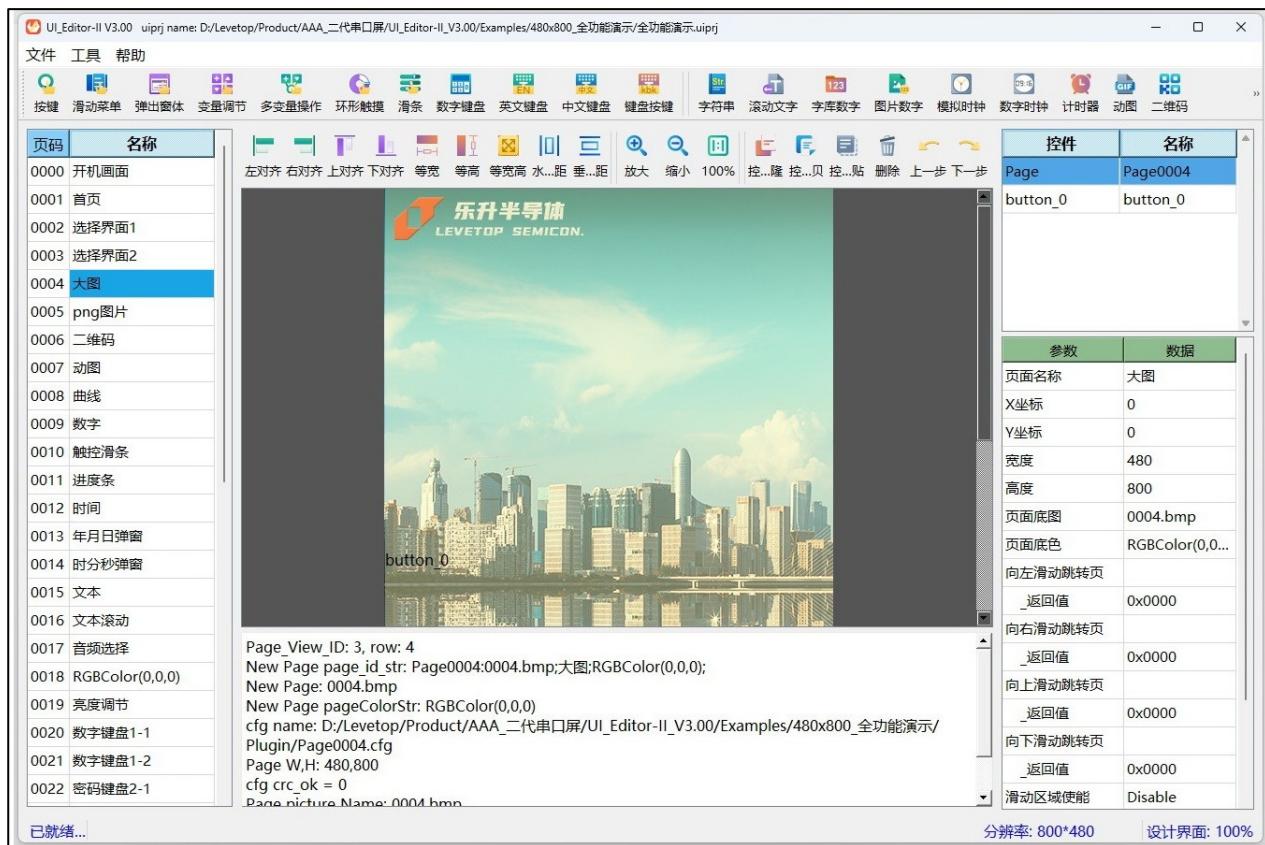

| 图 3-3: UI-Editor 工具画面 .....                     | 44 |

| 图 3-4: TFT 串口屏模块 .....                          | 44 |

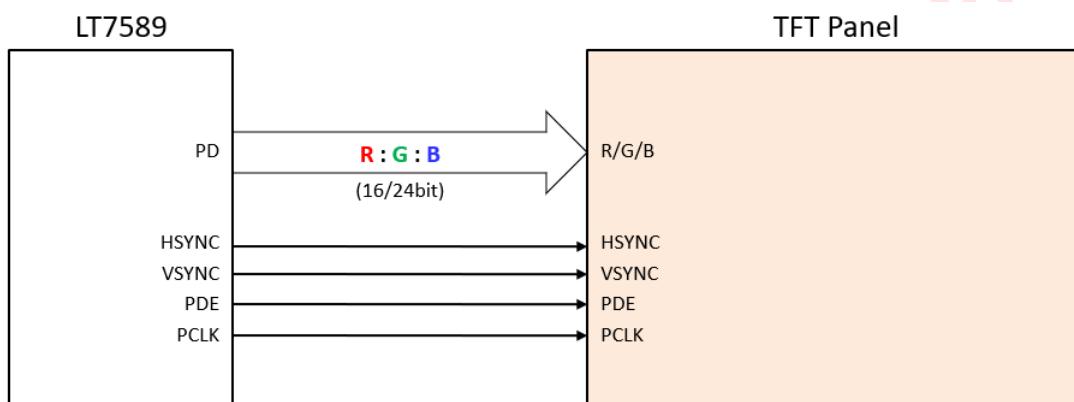

| 图 3-5: LT7589 与 TFT LCD 屏的连接 .....              | 46 |

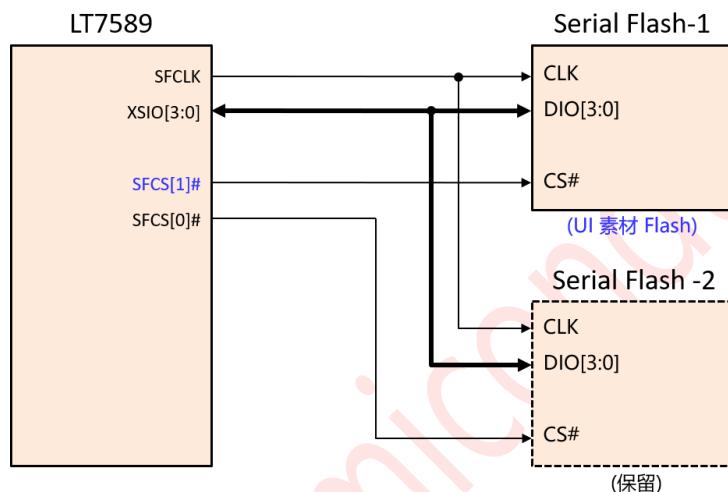

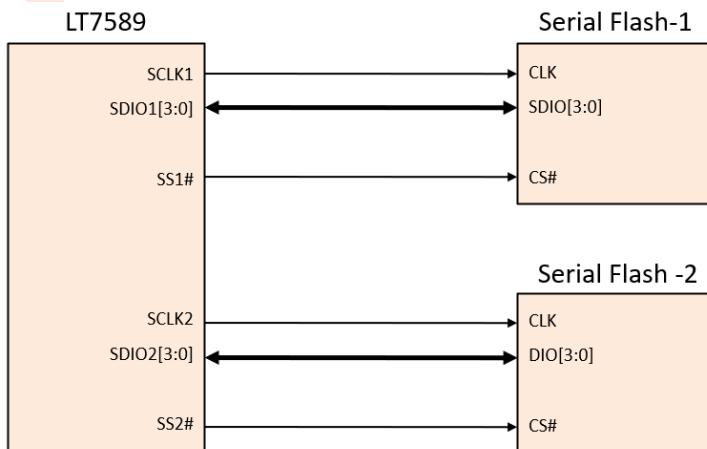

| 图 3-6: LT7589 存放素材的 QSPI Flash 连接示意图 .....      | 47 |

| 图 3-7: LT7589 MCU 端的 QSPI Flash 连接示意图 .....     | 47 |

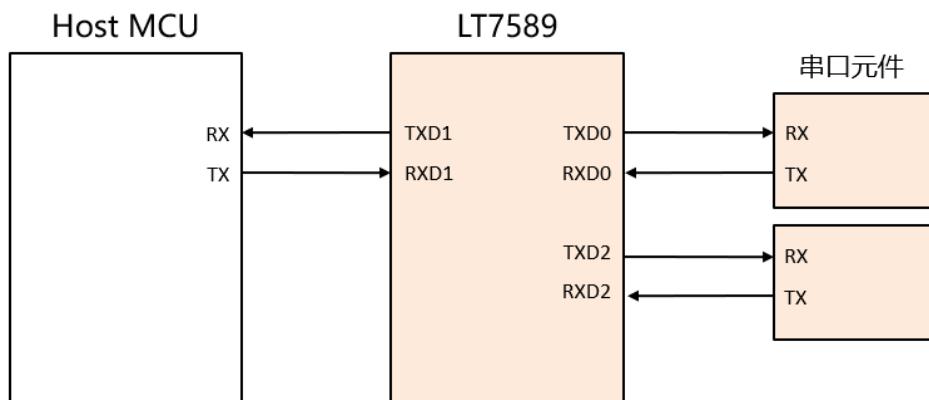

| 图 3-8: LT7589 提供 3 组 SCI 串口 .....               | 48 |

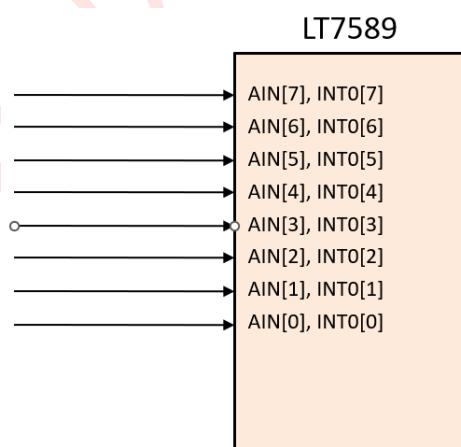

| 图 3-9: LT7589 提供 8 个模拟输入接口 .....                | 48 |

| 图 3-10: LT7589 MCU 端中断输入 .....                  | 49 |

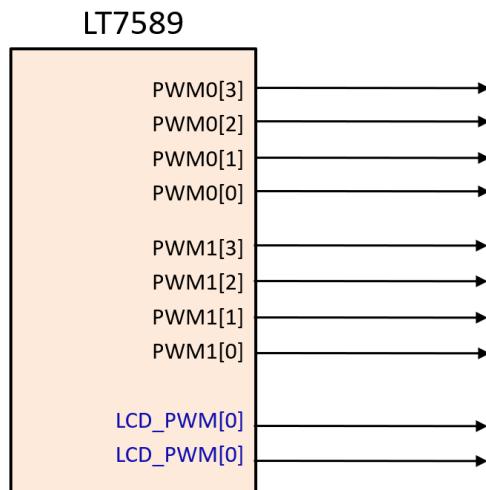

| 图 3-11: LT7589 MCU 端的 PWM 输出 .....              | 50 |

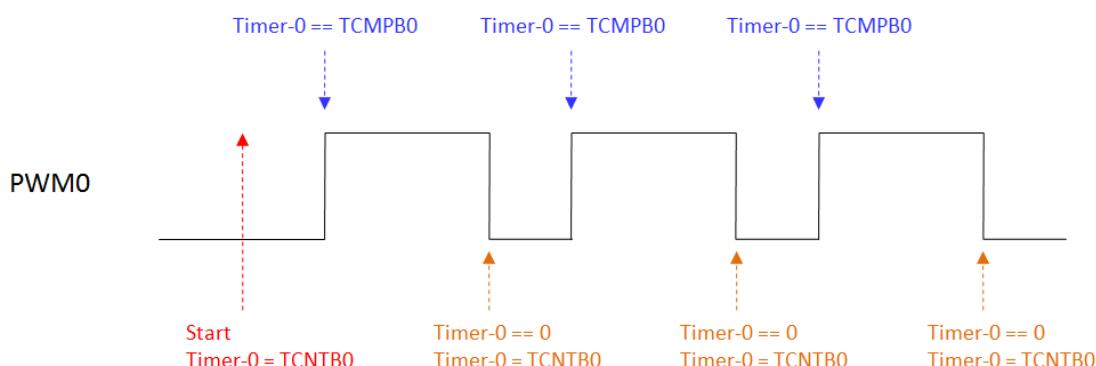

| 图 3-12: LCD_PWM 波形图 .....                       | 50 |

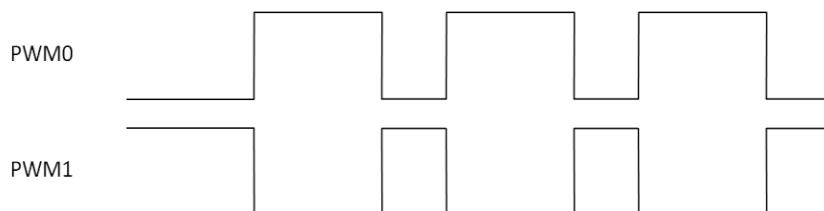

| 图 3-13: LCD_PWM[0] 和 LCD_PWM[1] 互补输出 .....      | 52 |

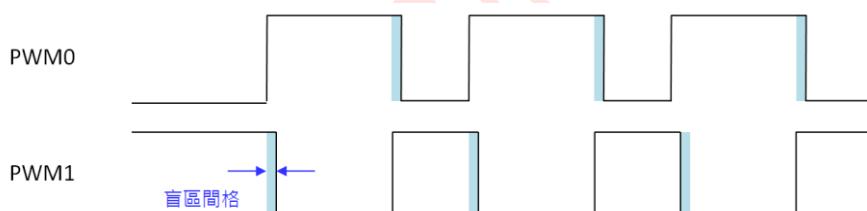

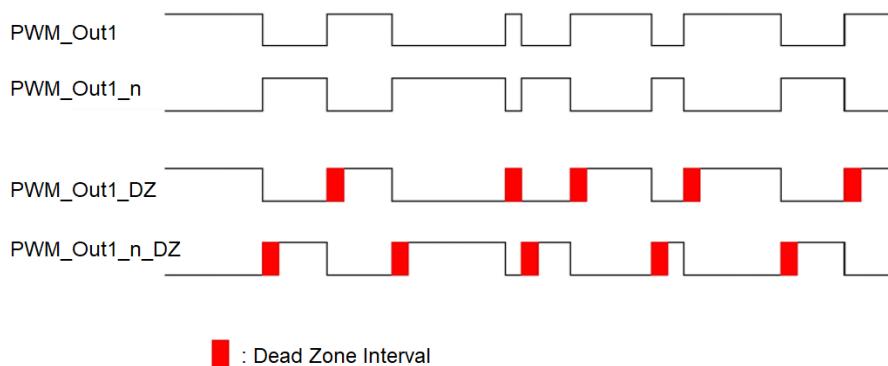

| 图 3-14: LCD_PWM[0] 和 LCD_PWM[1] 互补输出的盲区时序 ..... | 52 |

| 图 3-15: LT7589 USB 接口 .....                     | 53 |

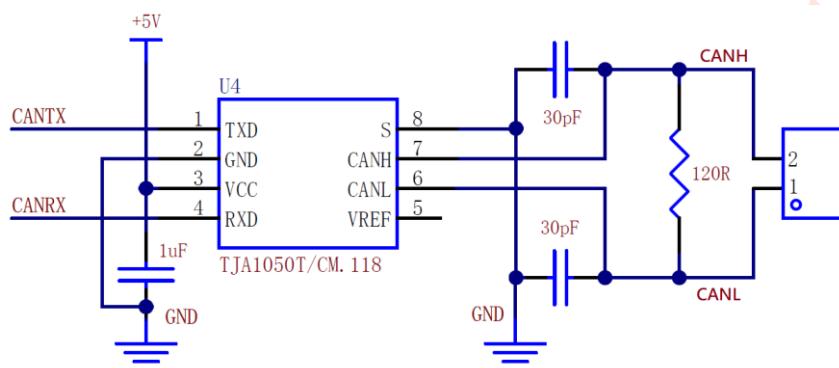

| 图 3-16: Canbus 接口应用范例 .....                     | 53 |

| 图 3-17: LT7589 时钟信号结构图 .....                    | 54 |

| 图 3-18: TFT 控制器使用外部 12MHz 晶振电路 .....            | 55 |

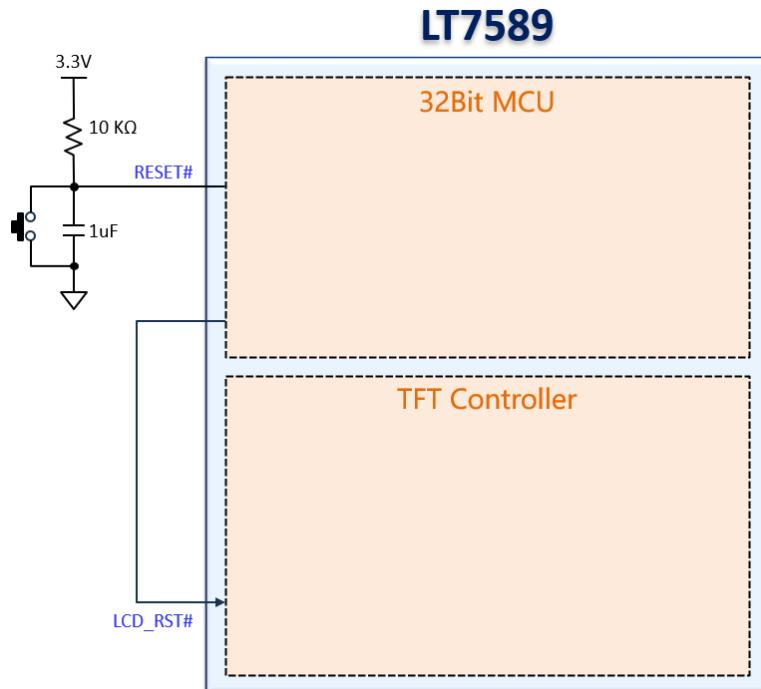

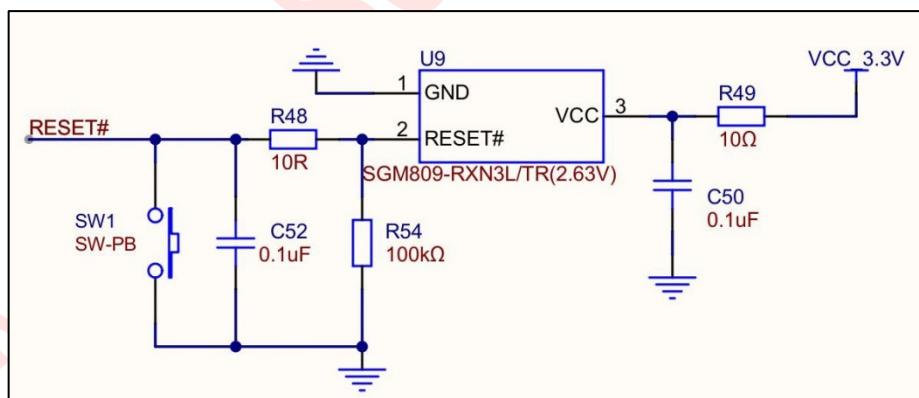

| 图 3-19: LT7589 复位信号结构图 .....                    | 56 |

| 图 3-20: 由复位芯片产生复位信号 .....                       | 56 |

| 图 4-1: 编程模型 .....                               | 58 |

| 图 4-2: 内存中的数据结构 .....                           | 59 |

| 图 4-3: 寄存器中的数据结构 .....                          | 59 |

| 图 5-1: 地址配置图 .....                              | 63 |

| 图 6-1: 唤醒配置寄存器 (WKUPC) .....                    | 66 |

| 图 6-2: 芯片引脚下拉配置寄存器 (CPPDC) .....                | 68 |

| 图 6-3: QSPI XIP 模式配置寄存器 (QSPI) .....            | 69 |

| 图 6-4: QSPI 32 位密钥寄存器 (QSPPIKEYR) .....         | 70 |

| 图 6-5: QSPI GPIO 配置寄存器 (QSPIGPIOCR) .....       | 70 |

| 图 6-6: MCU 访问 RAM 优先级配置寄存器 (MCURAMPROICR) ..... | 71 |

| 图 6-7: EPORT2 功能配置寄存器 (EPORT2FCR) .....         | 73 |

| 图 7-1: 中断控制状态寄存器 (ICSR) .....                   | 76 |

|                                                            |     |

|------------------------------------------------------------|-----|

| 图 7-2: 中断启用寄存器 (IER) .....                                 | 78  |

| 图 7-3: 中断等待集寄存器 (IPSR) .....                               | 79  |

| 图 7-4: 中断待定清除寄存器 (IPCR) .....                              | 80  |

| 图 7-5: 优先级选择寄存器 (PLSR0-PLSR31) .....                       | 81  |

| 图 7-6: 系统优先级级别选择寄存器 (SYSPLSR) .....                        | 82  |

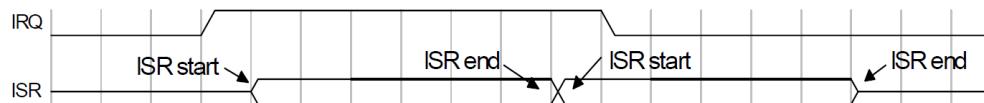

| 图 7-7: One Pulse Interrupt without Confliction .....       | 84  |

| 图 7-8: Level-sensitive Interrupt without Confliction ..... | 84  |

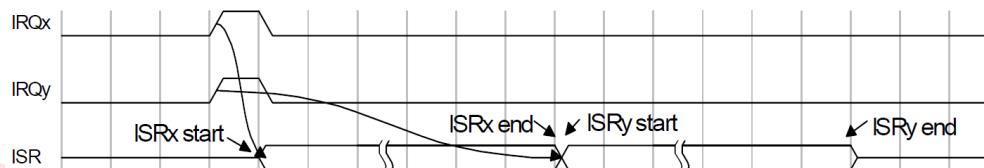

| 图 7-9: 同时发生两次中断.....                                       | 84  |

| 图 7-10: 具有冲突的较低优先级中断.....                                  | 85  |

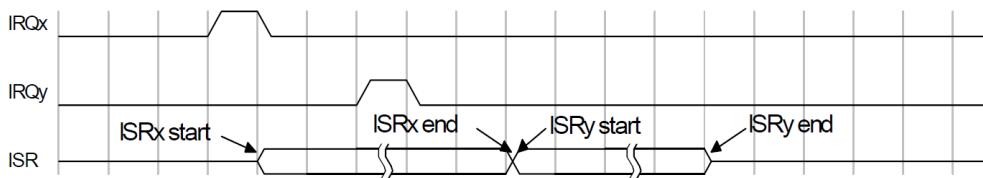

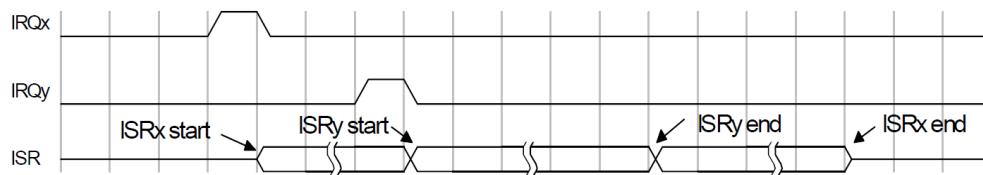

| 图 7-11: 具有冲突的更高优先级中断 .....                                 | 85  |

| 图 8-1: EPT 控制状态寄存器 (EPTCSR) .....                          | 92  |

| 图 8-2: EPT 重新加载寄存器 (EPTRLD) .....                          | 93  |

| 图 8-3: EPT 计数器寄存器 (EPTCNT) .....                           | 94  |

| 图 8-4: EPT 计数时序 .....                                      | 95  |

| 图 9-1: 时钟结构.....                                           | 96  |

| 图 9-2: 合成器控制寄存器 (SYNCR) .....                              | 99  |

| 图 9-3: 低速振荡器控制和状态寄存器 (LOSCCSR) .....                       | 103 |

| 图 9-4: PLL 配置和状态寄存器 (PLLCSR) .....                         | 105 |

| 图 9-5: 模块停止控制寄存器 (MSCR) .....                              | 107 |

| 图 9-6: EPT 外部时钟源启用控制寄存器 (ECSECR) .....                     | 109 |

| 图 9-7: OSC Bist 测试配置寄存器 1 (OBTCR1) .....                   | 110 |

| 图 9-8: OSC Bist 测试配置寄存器 2 (OBTCR2) .....                   | 111 |

| 图 9-9: OSC Bist 测试控制寄存器 (OBTCTLR) .....                    | 112 |

| 图 9-10: OSC Bist 测试计数器寄存器 (OBTCNTR) .....                  | 113 |

| 图 9-11: OSC Bist 测试结果寄存器 (OBTRR) .....                     | 114 |

| 图 10-1: 复位控制器的方块图 .....                                    | 116 |

| 图 10-2: 复位测试寄存器 (RTR) .....                                | 117 |

| 图 10-3: 复位状态寄存器 (RSR) .....                                | 118 |

| 图 10-4: 复位控制寄存器 (RCR) .....                                | 119 |

| 图 10-5: 复位控制流程.....                                        | 121 |

| 图 12-1: 高速缓存模块的方块图 .....                                   | 124 |

| 图 12-2: 高速缓存控制寄存器 (LMEM_CCR) .....                         | 126 |

| 图 12-3: 高速缓存线控制寄存器 (LMEM_CLCR) .....                       | 127 |

| 图 12-4: 高速缓存搜索地址寄存器 (LMEM_CSAR) .....                      | 129 |

| 图 12-5: 高速缓存读/写值寄存器 (LMEM_CCVR) .....                      | 130 |

| 图 12-6: 高速缓存访问寄存器 (LMEM_ACRG) .....                        | 131 |

| 图 12-7: 高速缓存页不验证基本地址寄存器 (LMEM_PAGE_INV_BADDR) .....        | 132 |

| 图 12-8: 高速缓存页面不验证大小寄存器 (LMEM_PAGE_INV_SIZE) .....          | 133 |

| 图 12-9: 高速缓存时钟启用寄存器 (LMEM_CACHE_CLK_EN) .....              | 134 |

| 图 12-10: 高速缓存标签和数据访问结构 .....                               | 135 |

|                                               |     |

|-----------------------------------------------|-----|

| 图 13-1: DMA 结构图 .....                         | 142 |

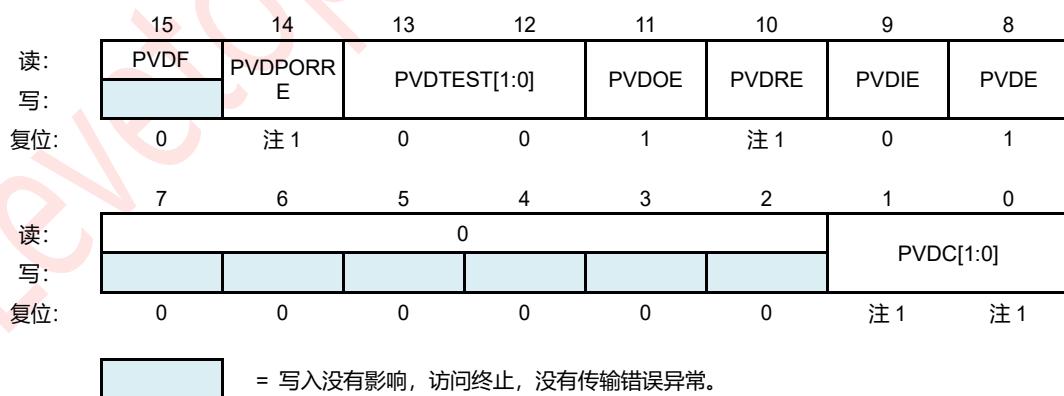

| 图 14-1: 可编程电压检测器配置寄存器 (PVDC) .....            | 144 |

| 图 14-2: 客户配置寄存器 (CCR) .....                   | 146 |

| 图 14-3: 外部高速振荡器稳定时间配置寄存器 (EOSCST) .....       | 149 |

| 图 14-4: PLL 锁定时间配置寄存器 (PLLOCKCR) .....        | 150 |

| 图 14-5: 复位引脚过滤器启用和值寄存器 (RFEVR) .....          | 150 |

| 图 14-6: 可编程电压检测器滤波器启用和值寄存器 (PVDFEVR) .....    | 151 |

| 图 14-7: 工厂配置寄存器 (FCR) .....                   | 152 |

| 图 14-8: ADC 信道禁用配置寄存器 (ADCCDISR) .....        | 153 |

| 图 14-9: VREF 修剪配置寄存器 (VREFTCR) .....          | 154 |

| 图 14-10: LDO1P2 修剪配置寄存器 (LDOTCR) .....        | 155 |

| 图 14-11: RTC 修剪配置寄存器 (RTCTCR) .....           | 156 |

| 图 15-1: PIT 方块图 .....                         | 157 |

| 图 15-2: PIT Modulus 寄存器 (PMR) .....           | 159 |

| 图 15-3: PIT 控制和状态寄存器 (PCSR) .....             | 159 |

| 图 15-4: PIT 计数寄存器 (PCNTR) .....               | 162 |

| 图 15-5: 计数器从 Modulus Latch 重新加载 .....         | 162 |

| 图 15-6: 在自由运行模式下的计数器 .....                    | 163 |

| 图 16-1: 看门狗计时器方块图 .....                       | 165 |

| 图 16-2: 看门狗模量寄存器 (WMR) .....                  | 166 |

| 图 16-3: 看门狗控制寄存器 (WCR) .....                  | 167 |

| 图 16-4: 看门狗服务寄存器 (WSR) .....                  | 169 |

| 图 16-5: 看门机构统计寄存器 (WCNTR) .....               | 169 |

| 图 17-1: RTC 方块图 .....                         | 170 |

| 图 17-2: RTC 应用电路 .....                        | 171 |

| 图 18-1: EPORT 方块图 .....                       | 172 |

| 图 18-2: EPORT 端口中断启用寄存器 (EPIER) .....         | 174 |

| 图 18-3: EPORT 数据方向寄存器 (EPDDR) .....           | 175 |

| 图 18-4: EPORT 引脚分配寄存器 (EPPAR) .....           | 175 |

| 图 18-5: EPORT 引脚上拉式启用寄存器 (EPPUE) .....        | 176 |

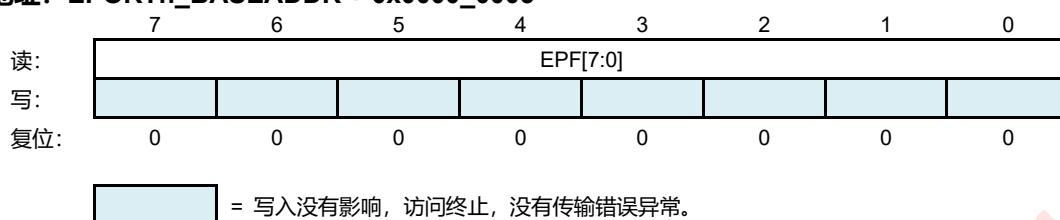

| 图 18-6: EPORT 端口标志寄存器 (EPFR) .....            | 177 |

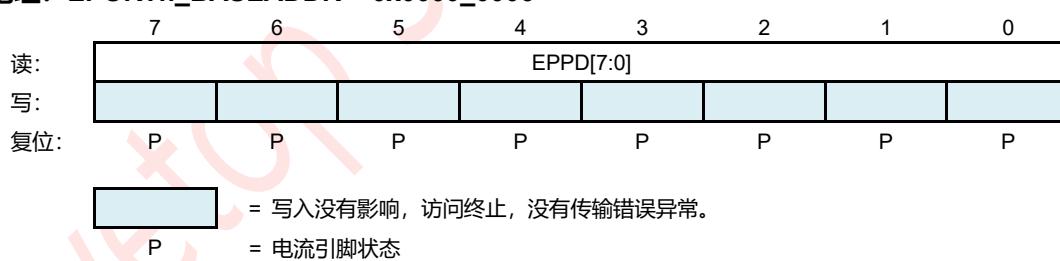

| 图 18-7: EPORT 端口引脚数据寄存器 (EPPDR) .....         | 177 |

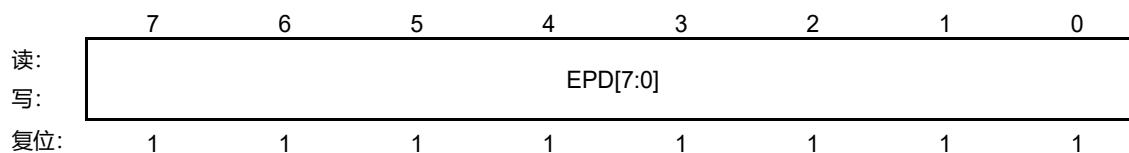

| 图 18-8: EPORT 端口数据寄存器 (EPDR) .....            | 178 |

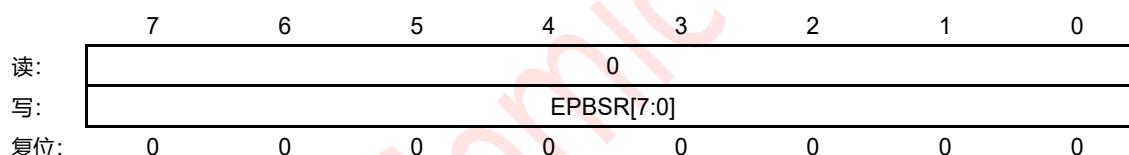

| 图 18-9: EPORT 端口位设置寄存器 (EPBSR) .....          | 178 |

| 图 18-10: EPORT 数字滤波器控制寄存器 (EPFC) .....        | 179 |

| 图 18-11: EPORT Open Drain 启用寄存器 (EPODE) ..... | 179 |

| 图 18-12: EPORT 级极性寄存器 (EPLPR) .....           | 180 |

| 图 18-13: EPORT 端口位清除寄存器 (EPBCR) .....         | 180 |

| 图 19-1: CANBus 方块图 .....                      | 181 |

| 图 19-2: Canbus 电路示例 .....                     | 184 |

|                                                       |     |

|-------------------------------------------------------|-----|

| 图 20-1: SCI 发送器方块图.....                               | 186 |

| 图 20-2: SCI 接收器方块图.....                               | 187 |

| 图 20-3: SCI 版本 ID 寄存器 (SCI_VERID) .....               | 189 |

| 图 20-4: SCI 参数寄存器 (SCI_PARAM) .....                   | 190 |

| 图 20-5: SCI 复位寄存器 (SCI_RESET) .....                   | 191 |

| 图 20-6: SCI 引脚寄存器 (SCI_PIN) .....                     | 192 |

| 图 20-7: SCI 波特率寄存器 (SCI_BAUD) .....                   | 193 |

| 图 20-8: SCI 状态寄存器 (SCI_STAT) .....                    | 195 |

| 图 20-9: SCI 控制寄存器 (SCI_CTRL) .....                    | 199 |

| 图 20-10: SCI 数据寄存器 (SCI_DATA) .....                   | 204 |

| 图 20-11: SCI 匹配地址寄存器 (SCI_MATCH) .....                | 206 |

| 图 20-12: SCI 调制解调器 IrDA 寄存器 (SCI_MODIR) .....         | 207 |

| 图 20-13: SCI FIFO 寄存器 (SCI_FIFO) .....                | 209 |

| 图 20-14: SCI 水印寄存器 (SCI_WATER) .....                  | 212 |

| 图 20-15: SCI 过采样比寄存器 (SCI_OSR) .....                  | 213 |

| 图 20-16: SCI 波特率生成.....                               | 214 |

| 图 21-1: SSI 方块图.....                                  | 225 |

| 图 21-2: SSI 应用图.....                                  | 225 |

| 图 21-3: 控制寄存器 0 (CTRLR0) .....                        | 227 |

| 图 21-4: 控制寄存器 1 (CTRLR1) .....                        | 230 |

| 图 21-5: SSI 启用寄存器 (SSIENR) .....                      | 231 |

| 图 21-6: 微线控制寄存器 (MWCR) .....                          | 232 |

| 图 21-7: 从属服务器启用寄存器 (SER) .....                        | 233 |

| 图 21-8: 波特率选择 (BAUDR) .....                           | 234 |

| 图 21-9: 传输 FIFO 阈值级别 (TXFTLR) .....                   | 235 |

| 图 21-10: 接收 FIFO 阈值级别 (RXFTLR) .....                  | 236 |

| 图 21-11: 传输 FIFO 液位寄存器 (TXFLR) .....                  | 237 |

| 图 21-12: 接收 FIFO 级别寄存器 (RXFLR) .....                  | 238 |

| 图 21-13: 状态寄存器 (SR) .....                             | 239 |

| 图 21-14: 中断掩码寄存器 (IMR) .....                          | 240 |

| 图 21-15: 中断状态寄存器 (ISR) .....                          | 242 |

| 图 21-16: 原始中断状态寄存器 (RISR) .....                       | 243 |

| 图 21-17: 传输 FIFO 溢出中断清除寄存器 (TXOICR) .....             | 244 |

| 图 21-18: 接收 FIFO 溢出中断清除寄存器 (RXOICR) .....             | 245 |

| 图 21-19: 接收 FIFO 下溢 (UnderFlow)中断清除寄存器 (RXUICR) ..... | 246 |

| 图 21-20: 中断清除寄存器 (ICR) .....                          | 247 |

| 图 21-21: DMA 控制寄存器 (DMACR) .....                      | 248 |

| 图 21-22: DMA 传输数据级别 (DMATDLR) .....                   | 249 |

| 图 21-23: DMA 接收数据级别 (DMARDLR) .....                   | 250 |

| 图 21-24: 识别寄存器 (IDR) .....                            | 251 |

|                                                |     |

|------------------------------------------------|-----|

| 图 21-25: 版本 ID 寄存器 (VIDR) .....                | 252 |

| 图 21-26: SSI 数据寄存器 (DRx) .....                 | 253 |

| 图 21-27: RX 取样延迟寄存器 (RXSDR) .....              | 254 |

| 图 21-28: SPI 控制寄存器 0 (SPICTRLR0) .....         | 255 |

| 图 21-29: XIP 模式位 (XIPMBR) .....                | 257 |

| 图 21-30: XIP 国际寄存器 (XIPIIR) .....              | 258 |

| 图 21-31: XIP 封装初始寄存器 (XIPWIR) .....            | 259 |

| 图 21-32: XIP 控制寄存器 (XIPCR) .....               | 260 |

| 图 21-33: XIP 从属服务器启用寄存器 (XIPSER) .....         | 262 |

| 图 21-34: XIP 接收 FIFO 溢出中断清除寄存器 (XRXIOCR) ..... | 263 |

| 图 21-35: XIP 连续传输超时寄存器 (XIPCTTOR) .....        | 264 |

| 图 21-36: SSI 配置为主设备 .....                      | 265 |

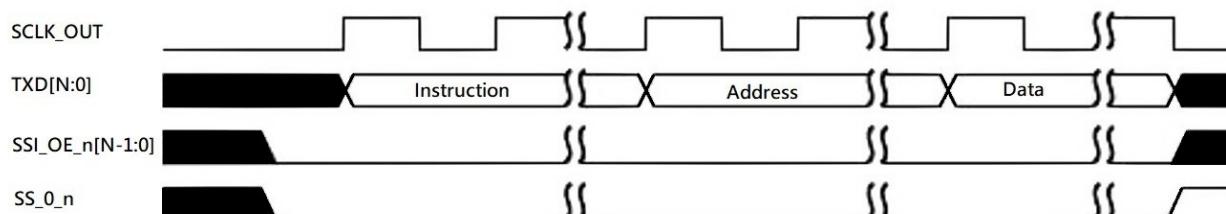

| 图 21-37: 典型的写入操作双/四/八进制 SPI 模式 .....           | 267 |

| 图 21-38: 典型的读取操作双/四/八进制 SPI 模式 .....           | 267 |

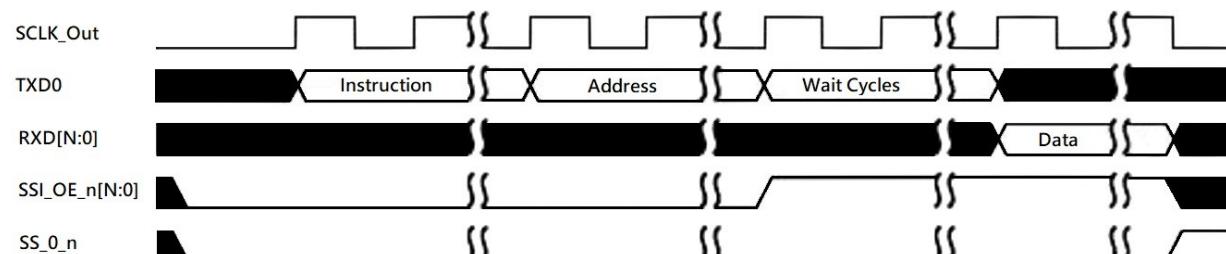

| 图 21-39: XIP 传输与指令阶段 .....                     | 268 |

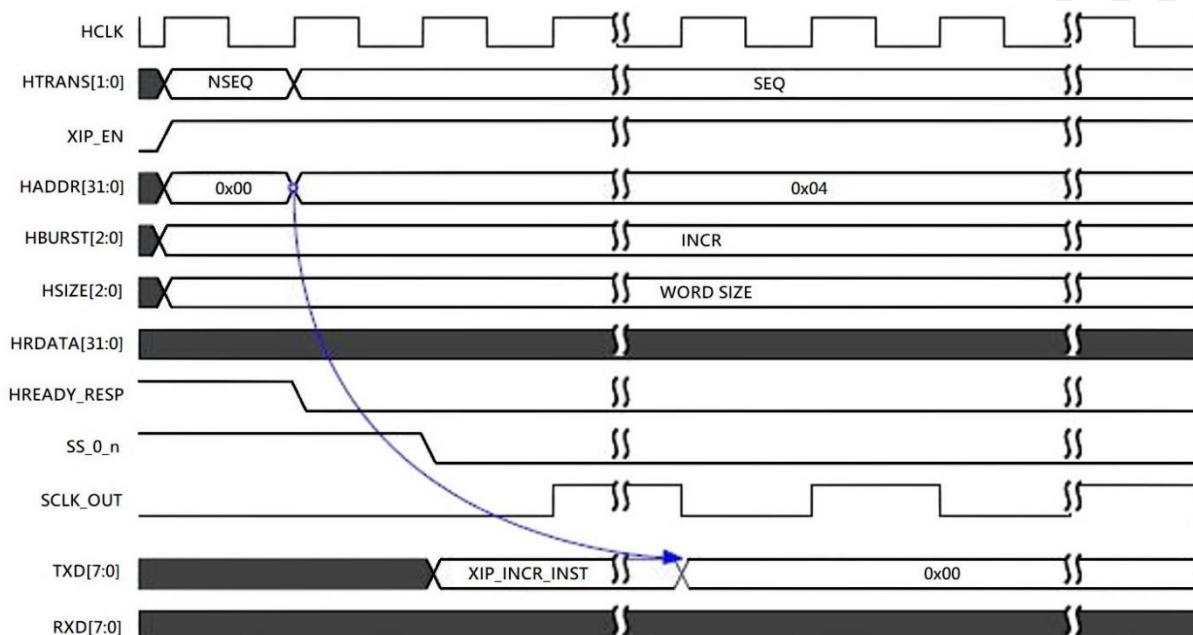

| 图 22-1: PWM 方块图 .....                          | 271 |

| 图 22-2: PWM 比例前寄存器 (PPR) .....                 | 273 |

| 图 22-3: PWM 时钟选择寄存器 (PCSR) .....               | 274 |

| 图 22-4: PWM 控制寄存器 (PCR) .....                  | 275 |

| 图 22-5: PWM 计数器寄存器 (PCNR) .....                | 279 |

| 图 22-6: PWM 比较器寄存器 (PCMR) .....                | 281 |

| 图 22-7: PWM 输出 .....                           | 282 |

| 图 22-8: PWM 占空比 .....                          | 282 |

| 图 22-9: PWM 计时器寄存器 (PTR) .....                 | 284 |

| 图 22-10: PWM 中断启用寄存器 (PIER) .....              | 285 |

| 图 22-11: PWM 中断标志寄存器 (PIFR) .....              | 286 |

| 图 22-12: PWM 捕获控制寄存器 (PCCR0) .....             | 287 |

| 图 22-13: PWM 捕获控制寄存器 (PCCR1) .....             | 288 |

| 图 22-14: PWM 捕获上升锁存寄存器 (PCRLR0) .....          | 289 |

| 图 22-15: PWM 捕获上升锁存寄存器 (PCRLR1) .....          | 290 |

| 图 22-16: PWM 捕获上升锁存寄存器 (PCRLR2) .....          | 290 |

| 图 22-17: PWM 捕获上升锁存寄存器 (PCRLR3) .....          | 291 |

| 图 22-18: PWM 捕获下降锁存寄存器 (PCFLR0) .....          | 292 |

| 图 22-19: PWM 捕获下降锁存寄存器 (PCFLR13) .....         | 292 |

| 图 22-20: PWM 捕获下降锁存寄存器 (PCFLR2) .....          | 293 |

| 图 22-21: PWM 捕获下降锁存寄存器 (PCFLR3) .....          | 293 |

| 图 22-22: PWM 端口控制寄存器 (PPCR) .....              | 294 |

| 图 22-23: PWM 双缓冲功能说明 .....                     | 295 |

| 图 22-24: PWM 控制器输出负荷比 .....                    | 295 |

| 图 22-25: 死区生成操作 .....                          | 296 |

|                                                |     |

|------------------------------------------------|-----|

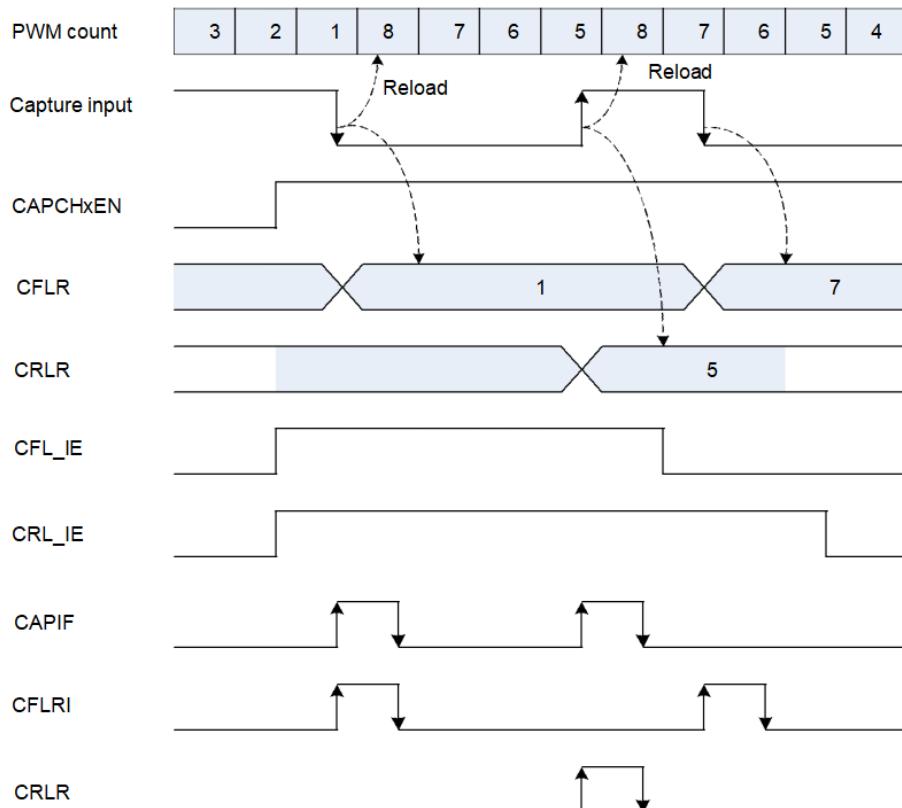

| 图 22-26: 捕获基本计时器操作.....                        | 297 |

| 图 23-1: 比较器方块图.....                            | 298 |

| 图 23-2: 比较器控制寄存器 (CPTCN) .....                 | 300 |

| 图 23-3: 比较器模式选择寄存器 (CPTMD) .....               | 301 |

| 图 23-4: 比较器 MUX 选择寄存器 (CPTMX) .....            | 302 |

| 图 23-5: 比较器输出过滤器选择寄存器 (CPTFLS) .....           | 303 |

| 图 23-6: 比较器滞后图.....                            | 304 |

| 图 24-1: USB 全速设备(USB 模块) 方块图.....              | 306 |

| 图 24-2: USBPHY 控制寄存器 1 (USBPHY_CTRL1) .....    | 308 |

| 图 24-3: 中断状态寄存器 (INT_STAT) .....               | 309 |

| 图 24-4: 中断启用寄存器 (INT_ENB) .....                | 310 |

| 图 24-5: 错误中断状态寄存器 (ERR_STAT) .....             | 312 |

| 图 24-6: 错误中断启用寄存器 (ERR_ENB) .....              | 313 |

| 图 24-7: 状态寄存器 (STAT) .....                     | 315 |

| 图 24-8: 控制寄存器 (CTL) .....                      | 316 |

| 图 24-9: 地址寄存器 (ADDR) .....                     | 318 |

| 图 24-10: EBT 页面寄存器 1 (EBT_PAGE_01) .....       | 319 |

| 图 24-11: 帧号寄存器 (FRMNUML) .....                 | 320 |

| 图 24-12: 帧号寄存器 (FRMNUMH) .....                 | 321 |

| 图 24-13: TOKEN 寄存器 (TOKEN) .....               | 322 |

| 图 24-14: SOF 阈值寄存器 (SOF_THLD) .....            | 323 |

| 图 24-15: EBT 页面寄存器 2 (EBT_PAGE_02) .....       | 324 |

| 图 24-16: EBT 页面寄存器 3 (EBT_PAGE_03) .....       | 325 |

| 图 24-17: 端点控制寄存器 (ENDPTn, n = 0-7) .....       | 326 |

| 图 24-18: USBPHY 控制寄存器 2 (USBPHY_CTRL2) .....   | 327 |

| 图 24-19: USB PHY 观察寄存器 (USB_PHY_OBSERVE) ..... | 328 |

| 图 24-20: USB PHY GPIO 寄存器 (USB_PHY_GPIO) ..... | 329 |

| 图 24-21: USB 简历启用寄存器 (USB_RESMEN) .....        | 330 |

| 图 24-22: USB PHY 控制寄存器 3 (USBPHY_CTRL3) .....  | 331 |

| 图 24-23: USB PHY 控制寄存器 4 (USBPHY_CTRL4) .....  | 332 |

| 图 24-24: 端点缓冲区表.....                           | 334 |

| 图 24-25: USB Token Transaction .....           | 338 |

| 图 25-1: ADC 方块图.....                           | 341 |

| 图 25-2: 启用/禁用 ADC .....                        | 342 |

| 图 25-3: ADC 时钟方案 .....                         | 343 |

| 图 25-4: Analog to Digital 转换时间.....            | 346 |

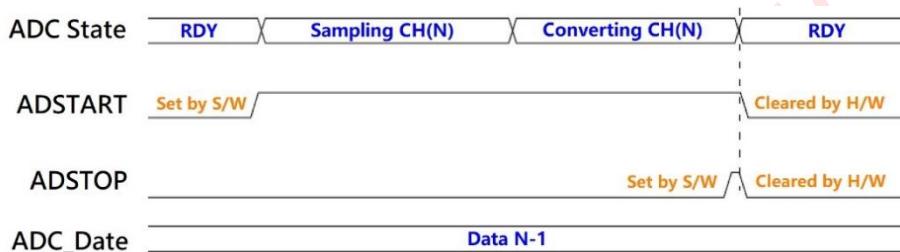

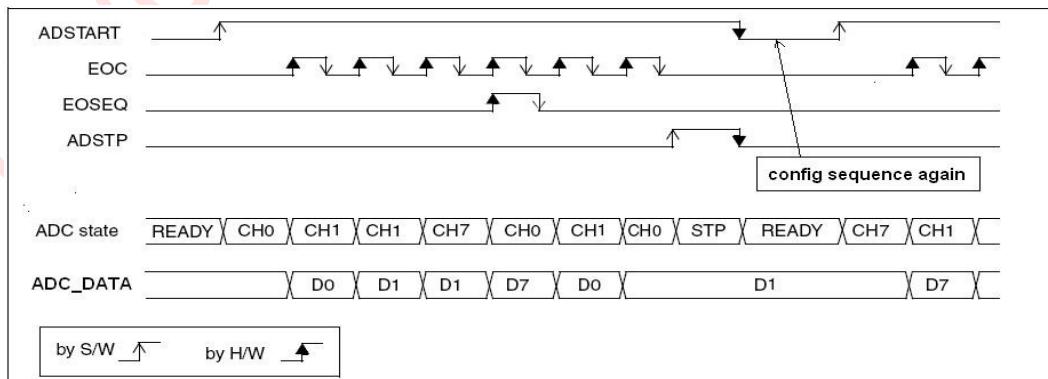

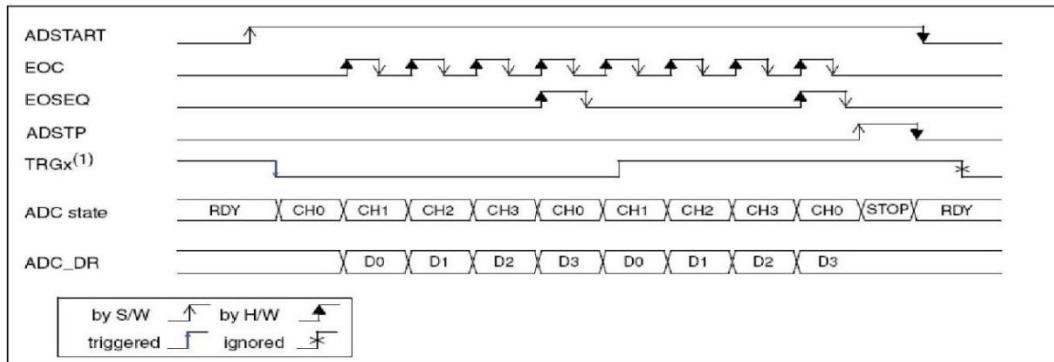

| 图 25-5: 停止一个正在进行的转换 .....                      | 347 |

| 图 25-6: 一个序列的单一转换, 软件触发器 .....                 | 350 |

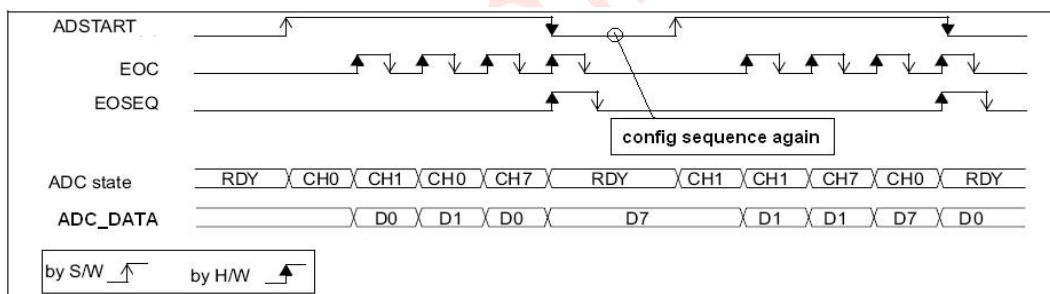

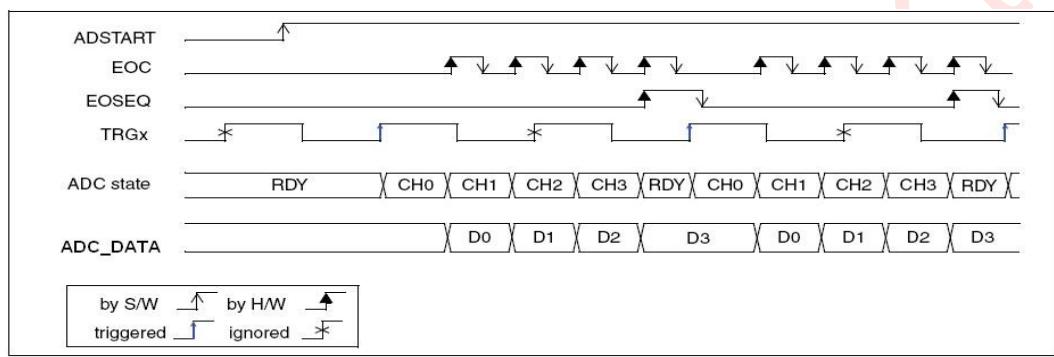

| 图 25-7: 一个序列的连续转换, 软件触发器 .....                 | 350 |

| 图 25-8: 一个序列的单一转换, 硬件触发器 .....                 | 351 |

|                                            |     |

|--------------------------------------------|-----|

| 图 25-9: 一个序列的连续转换, 硬件触发器 .....             | 351 |

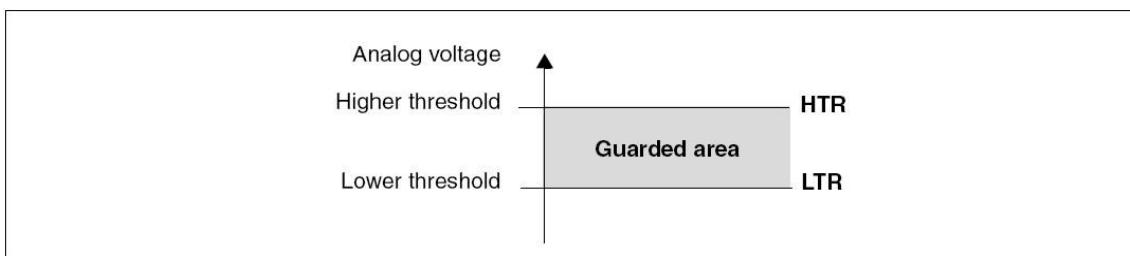

| 图 25-10: 模拟式看门狗的监视区域 .....                 | 355 |

| 图 25-11: ADC 中断和状态寄存器 (ADC_ISR) .....      | 357 |

| 图 25-12: ADC 中断启用寄存器 (ADC_IER) .....       | 359 |

| 图 25-13: ADC 控制寄存器 (ADC_CR) .....          | 360 |

| 图 25-14: ADC 配置寄存器 1 (ADC_CFGR1) .....     | 362 |

| 图 25-15: ADC 配置寄存器 2 (ADC_CFGR2) .....     | 364 |

| 图 25-16: ADC 采样时间寄存器 (ADC_SMPR) .....      | 365 |

| 图 25-17: ADC 看门狗寄存器 (ADC_WDG) .....        | 366 |

| 图 25-18: ADC 看门狗阈值寄存器 (ADC_TR) .....       | 367 |

| 图 25-19: ADC 通道选择寄存器 1 (ADC_CHSELR1) ..... | 368 |

| 图 25-20: ADC 通道选择寄存器 2 (ADC_CHSELR2) ..... | 368 |

| 图 25-21: ADC FIFO 访问寄存器 (ADC_FIFO) .....   | 369 |

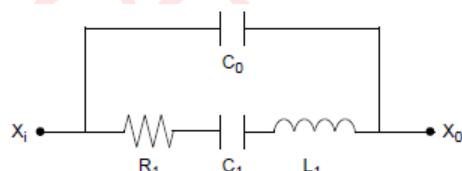

| 图 27-1: 晶振等效电路图 .....                      | 376 |

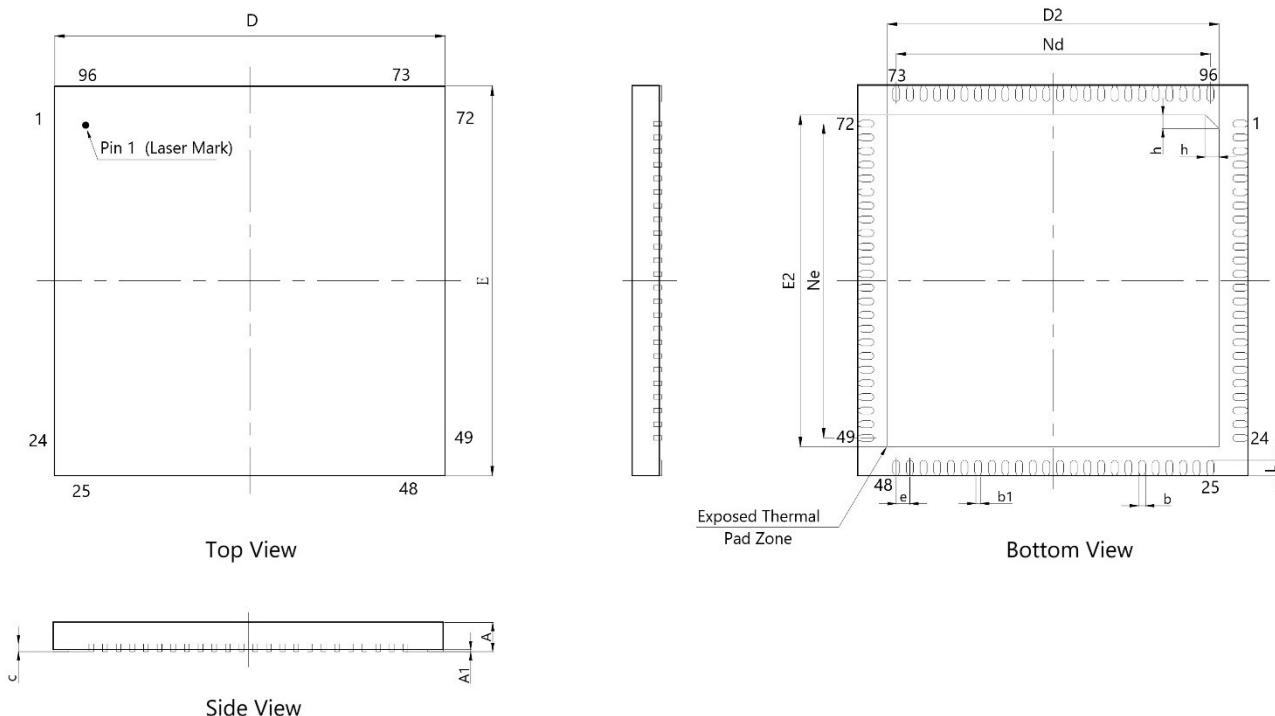

| 图 28-1: QFN-96Pin 外观尺寸图 .....              | 378 |

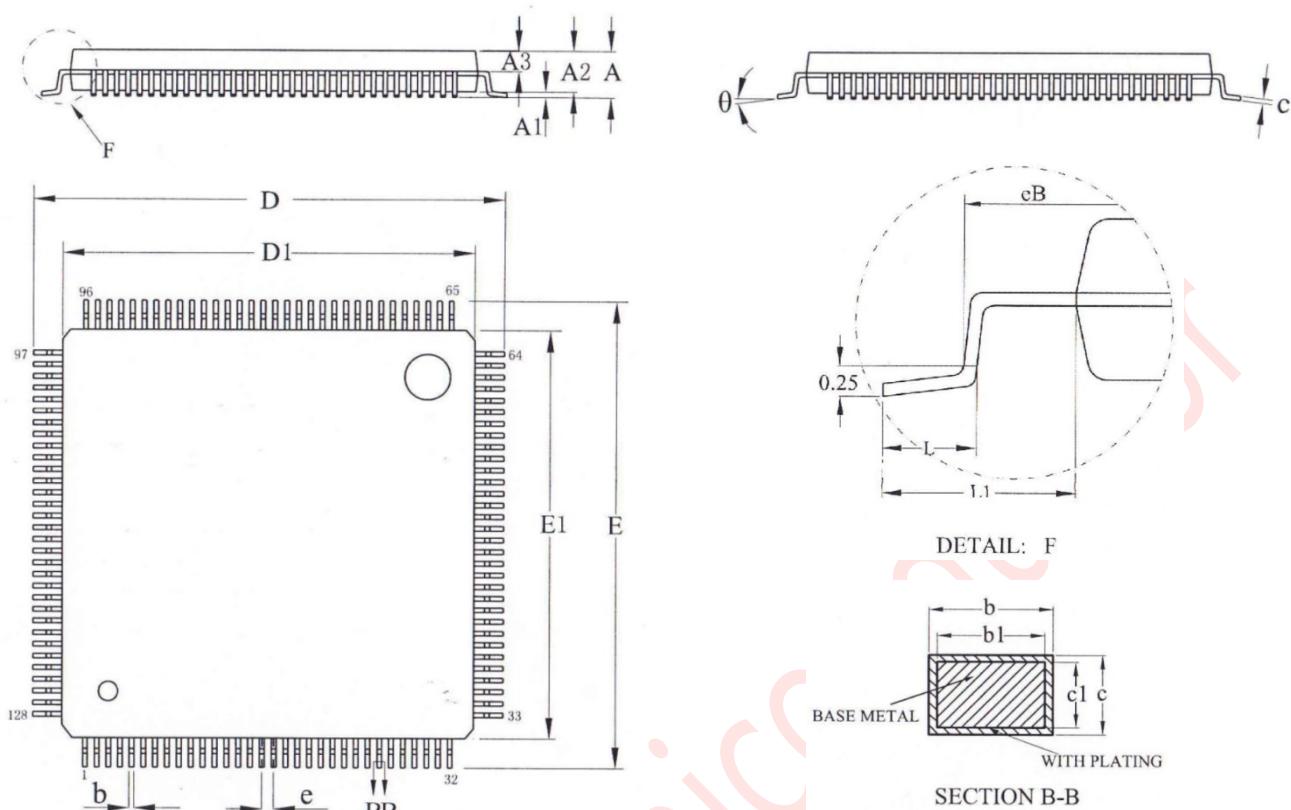

| 图 28-2: LQFP-128Pin 外观尺寸图 .....            | 379 |

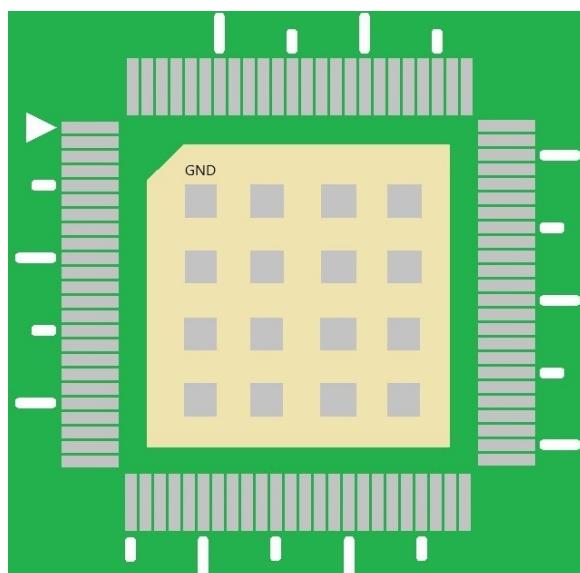

| 图 28-3: LT7589A 底部焊盘 PCB 的设计建议-1 .....     | 380 |

| 图 28-4: LT7589A 底部焊盘 PCB 的设计建议-2 .....     | 380 |

| 图 29-1: LT7589A 参考原理图 .....                | 381 |

| 图 29-2: LT7589B 参考原理图 .....                | 382 |

## 表 列 表

|                                      |     |

|--------------------------------------|-----|

| 表 1-1: 型号说明 .....                    | 25  |

| 表 2-1: SCI (Uart) 串口信号 .....         | 30  |

| 表 2-2: LCD 屏接口信号 .....               | 31  |

| 表 2-3: QSPI 信号 .....                 | 32  |

| 表 2-4: 外部串行 Flash 信号 .....           | 33  |

| 表 2-5: PWM 信号 .....                  | 34  |

| 表 2-6: USB 接口信号 .....                | 35  |

| 表 2-7: 中断信号 .....                    | 36  |

| 表 2-8: ADC 模拟输入信号 .....              | 38  |

| 表 2-9: 其他控制信号 .....                  | 38  |

| 表 2-10: 电源与时钟信号 .....                | 39  |

| 表 2-11: LT7589A IO 口资源数量表 .....      | 41  |

| 表 2-12: LT7589B IO 口资源数量表 .....      | 42  |

| 表 3-1: UI_Editor-III 串口通信与指令差异 ..... | 45  |

| 表 3-2: UI_Editor-III 串口通信指令格式 .....  | 45  |

| 表 3-3: RGB 数据与颜色深度 .....             | 46  |

| 表 3-4: GPIO 接口与其他控制信号共享脚位 .....      | 49  |

| 表 3-5: 寄存器 REG[85h] 说明 .....         | 51  |

| 表 4-1: 32 位 RISC 指令集 .....           | 60  |

| 表 5-1: 硬件模块与寄存器地址的配置图 .....          | 64  |

| 表 6-1: CCM 内存映射 .....                | 65  |

| 表 6-2: WKUPSEN 和相应的唤醒源 .....         | 66  |

| 表 6-3: 芯片引脚下拉配置 .....                | 68  |

| 表 6-4: EPORT2 功能控制位 .....            | 73  |

| 表 7-1: 中断控制器模块内存映射 .....             | 74  |

| 表 7-2: 优先值调整 .....                   | 81  |

| 表 7-3: 优先值调整 .....                   | 82  |

| 表 7-4: 优先值调整 .....                   | 83  |

| 表 7-5: 中断来源分配 .....                  | 86  |

| 表 8-1: 可编程定时器模块内存配置 .....            | 91  |

| 表 9-1: 时钟内存映射 .....                  | 98  |

| 表 9-2: PLL 时钟分频器 .....               | 100 |

| 表 9-3: ADC 时钟分频器 .....               | 101 |

| 表 9-4: CLKOUTSEL 模式 .....            | 102 |

| 表 9-5: 睡眠模块中的睡眠操作控制位 .....           | 102 |

| 表 9-6: PLL 输入分频数值 .....              | 106 |

| 表 9-7: PLL VCO 输出时钟的除频数值 .....       | 106 |

| 表 9-8: PLL 反馈的除频器数值 .....            | 107 |

|                                         |     |

|-----------------------------------------|-----|

| 表 9-9: MS[29:0] 相应的模块.....              | 108 |

| 表 9-10: EPT 时钟分频器.....                  | 109 |

| 表 10-1: 复位控制器地址映像.....                  | 117 |

| 表 10-2: 复位源汇总.....                      | 120 |

| 表 12-1: 高速缓存模块内存映射 .....                | 125 |

| 表 12-2: 缓存集命令 .....                     | 136 |

| 表 12-3: 缓存行命令 .....                     | 138 |

| 表 12-4: 行命令结果.....                      | 139 |

| 表 13-1: DMA 通道分配.....                   | 141 |

| 表 14-1: 寄存器内存映射.....                    | 144 |

| 表 14-2: 可编程电压检测器.....                   | 146 |

| 表 14-3: RGB 接口启用控制.....                 | 146 |

| 表 14-4: 编程调试接口控制.....                   | 147 |

| 表 14-5: RSTOUT 禁用控制.....                | 147 |

| 表 14-6: CLKOUT 禁用控制 .....               | 148 |

| 表 14-7: QSPI2 接口启用控制.....               | 148 |

| 表 14-8: ADC 通道禁用控制 .....                | 154 |

| 表 15-1: 可编程中断定时器模块内存映射.....             | 158 |

| 表 15-2: Prescaler Select Encoding ..... | 160 |

| 表 15-3: PIT 中断请求.....                   | 163 |

| 表 16-1: 看门狗计时器模块记忆地图.....               | 165 |

| 表 16-2: 看门狗计时器 Prescaler .....          | 168 |

| 表 18-1: 模块内存映射 .....                    | 173 |

| 表 18-2: EPPAx Field Settings.....       | 176 |

| 表 19-1: CANBus 信号.....                  | 183 |

| 表 20-1: 信号属性 .....                      | 187 |

| 表 20-2: SCI 模块记忆地图 .....                | 188 |

| 表 20-3: 断开字符长度 .....                    | 216 |

| 表 20-4: 接收器唤醒选项 .....                   | 217 |

| 表 21-1: SSI 内存映射 .....                  | 226 |

| 表 22-1: PWM 信号描述 .....                  | 271 |

| 表 22-2: 模块内存映射 .....                    | 272 |

| 表 22-3: 计时器 3 时钟源选择 .....               | 274 |

| 表 23-1: 比较器模块内存贴图 .....                 | 299 |

| 表 23-2: 比较器模式选择 .....                   | 301 |

| 表 23-3: 比较器负向输入 MUX 选择 .....            | 302 |

| 表 23-4: 比较器正输入 MUX 选择 .....             | 302 |

| 表 24-1: USB 模块内存地图 .....                | 307 |

| 表 24-2: 端点启用/方向控制 .....                 | 327 |

| 表 24-3: USB PHY 振荡器模式选择 .....           | 333 |

|                                              |     |

|----------------------------------------------|-----|

| 表 24-4: USB 目标设备的数据方向.....                   | 334 |

| 表 24-5: EBT Address Calculation Fields.....  | 335 |

| 表 24-6: 端点缓冲区表字节格式 .....                     | 336 |

| 表 24-7: 端点缓冲区表字节字段 .....                     | 336 |

| 表 24-8: USB 响应的 DMA 覆盖错误.....                | 339 |

| 表 25-1: 通道解码 .....                           | 344 |

| 表 25-2: 正在配置触发器的极性。 .....                    | 347 |

| 表 25-3: 配置触发器的极性.....                        | 348 |

| 表 25-4: 数据对齐和分辨率.....                        | 352 |

| 表 25-5: 模拟监控器通道选择 .....                      | 355 |

| 表 25-6: ADC 中断.....                          | 355 |

| 表 25-7: ADC 模块内存映射 .....                     | 356 |

| 表 27-1: 电气极限参数表 .....                        | 375 |

| 表 27-2: DC 电气参数表 .....                       | 375 |

| 表 27-3: 电源特性 .....                           | 377 |

| 表 27-4: 热阻参数 (Thermal Characteristics) ..... | 377 |

| 表 27-5: ESD 保护规格 .....                       | 377 |

| 表 28-1: QFN-96Pin 尺寸参数 .....                 | 378 |

| 表 28-2: LQFP-128Pin 尺寸参数.....                | 379 |

## 1. 芯片介绍

### 1.1. 基本简介

**LT7589** 是一款高效能 Uart TFT 串口屏控制芯片。内部结合了 32-bits RISC MCU 及具有 TFT LCD 图形显示控制器的 GUI (Graphical User Interface)，主要的功能就是提供 Uart 串口通讯，让主控端 MCU 透过简易的串口指令就能轻易的将要显示的信息呈现到 TFT 屏上。LT7589 内部硬件还提供 JPG 图片解码、PIP (Picture-in-Picture)、几何图形绘图等功能，能够提升 TFT 屏显示效率，及降低 MCU 处理图形显示所花费的时间，LT7589 支持的显示分辨率由 480\*480 (QVGA) 到 1280\*800，用于 16/24-bits 的 RGB 接口显示屏。

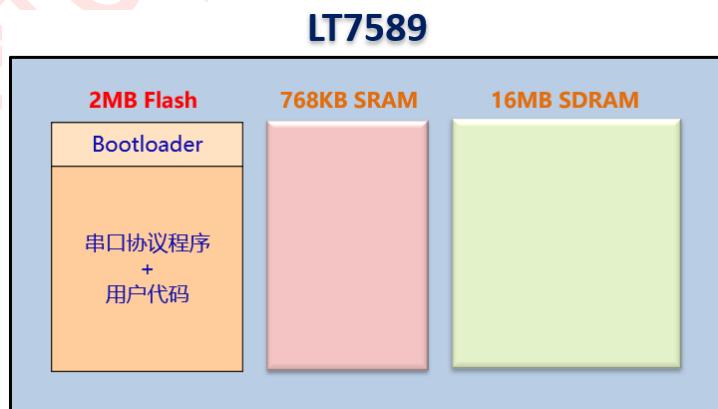

LT7589 内部的 MCU 主频最高为 200MHz，含有 2MB Flash、768KB SRAM、16MB 显示内存，并结合 **JPG 解码器**、2D 图形加速显示器、DMA 数据读取、与高速 **QSPI**

**Flash 接口**，用来快速读取储存在外部 QSPI Flash 的图片、动画、字库等信息，具有良好的显示效能。LT7589 可以配合 乐升半导体 开发的 UI 编辑软件 (UI\_Editor)、模拟软件 (UI\_Emulator)，直接在电脑上将设计好的 UI 素材与显示交互逻辑进行导入与显示界面开发，其所支持的显示功能包括图片显示、动画显示、滑动菜单显示、进度条显示、字符串显示、中英文键盘、数字键盘、模拟时钟、数字时钟、指针显示、二维码生成、多国语言、音频播放、变量控制，及结合触控屏或编码器功能的控制效果等等。除了串口屏 Uart 通讯接口，LT7589 还提供多组的 SCI (Uart) 接口可以连接如蓝牙模块、WiFi 模块等元件，也提供 **CanBus**、SD 卡 (SPI 模式)，模拟输入 AIN、PWM 及 INT 中断等接口，还自带 RTC 时钟。亦可用于 Little VGL 的 GUI 图形开发，具有良好的流畅度与极高的性价比。

由于含有高容量的 Flash 及 SRAM，LT7589 也可以作为一个带 TFT 控制器的主控 MCU 来使用，将主控及 TFT 显示功能由一颗 LT7589 来完成，它的显示功能非常适合用在 1280x800 分辨率以下带 TFT-LCD 屏的电子产品上，或用来取代原单色屏产品，提升产品达到智能化显示信息、增加产品质感、档次。LT7589 强大的显示功能非常适合用在有 TFT-LCD 屏的电子产品上，如各式智慧家电、汽车仪表盘、摩托车面板、多功能事务机、工业控制、电子仪器、医疗美容设备、检测设备、充电设备、逆变器、UPS 等电源设备、音响设备、及带屏智能音箱、机器人等产品。

### 1.2. 系统应用方块图

图 1-1：LT7589 设置在模块板上

图 1-2：LT7589 设置在系统主板上

图 1-3：LT7589 应用架构

### 1.3. 内部方块图

图 1-4: LT7589 内部方块图

表 1-1: 型号说明

| 型号      | 封装       | 内建显示内存 | 分辨率      | 色彩                      |

|---------|----------|--------|----------|-------------------------|

| LT7589A | QFN-96   | 128Mb  | 1280*800 | 16.7M 色<br>αRGB 8:8:8:8 |

| LT7589B | LQFP-128 | 128Mb  | 1280*800 | 16.7M 色<br>αRGB 8:8:8:8 |

## 1.4. 功能简介

### 主控端 MCU 界面

- 支持 Uart、USB 接口。

- 内建高效能 32-bits MCU、主频为 180MHz, 最高可达 200MHz。

### USB 界面

- 支持 USB2.0 Full Speed。

### SCI (Uart)界面

- 提供 3 组 SCI (Serial Communications Interface)。

- 可连接外部 SCI 接口之元件或是模块。

### 内存

- MCU 内建 2M bytes Flash。

- MCU 内建 512K+256K bytes SRAM。

- TFT 控制器内建 128Mb 的显示内存 (Display RAM)。

### 显示色彩数据格式

- 16bpp : 彩色 RGB 5:6:5 (2bytes/像素)。

- 24bpp : 彩色 RGB 8:8:8 (3bytes/像素或是 4bytes/像素)。

- αRGB 4:4:4:4 (4,096 索引色/像素, 含透明度属性)

- 32bpp : 彩色 αRGB 8:8:8:8 (4bytes/像素)。

### 面板接口与分辨率

- 支持 16、24-bits RGB 接口面板。

- 采用裸机开发时支持的分辨率：

- VGA : 640\*480 TFT 屏

- WVGA : 800\*480 TFT 屏

- SVGA : 800\*600 TFT 屏

- XGA : 1024\*768 TFT 屏

- SXGA : 1280\*1024 TFT 屏

- 串口屏开发时支持最大分辨率: 1280\*800。

### 显示功能

- 内建 JPG 硬件解码器

- 支持使用者可自行定义 4 个 32\*32 的图形光标。

- 提供虚拟显示功能: 虚拟显示可显示大于 LCD 面板大小的图像, 这样图像可以在任何方向上轻松滚动。

- 提供画中画 (PIP) 显示: 支持两个 PIP 视窗区域: 启用的 PIP 视窗显示在主视窗的上层, 而 PIP1 视窗显示在 PIP2 视窗的上层。

- 支持多重显示功能: 可以在显示缓冲区之间切换主显示视窗, 达到简单的动画显示效果。

- 支持唤醒时迅速显图像功能。

- 支持镜像和垂直翻转显示功能。

- 彩带显示 (Color Bar Display) : 在没有对内部显示内存写入数据的情况下仍然可以以彩带的方式显示, 默认分辨率为 640\*480 像素。

### 区块传输引擎 (BitBLT)

- 内建 2D BitBLT 引擎。

- 提供带光栅运算的复制图像功能。

- 提供颜色深度转换。

- 实心填充和图案填充功能:

- 提供用户定义的 8\*8 图像或 16\*16 图像。

- 提供两个图像合成一个图像功能:

- 色度键控功能 (Chroma-Keying) : 根据透明度将图像与指定的 RGB 颜色混合。

- 图形混合透明模式 (Window Alpha - Blending) : 根据指定区域内的透明度将两个图像混合。

- 像素混合透明模式 (Dot Alpha - Blending) : 根据 RGB 格式及透明度将两个图像混合。

### 几何图形加速器

- 提供画点、线、曲线、椭圆、三角形、矩形、圆角矩形等绘图功能。

## 显示文字功能

- 内建 ISO/IEC 8859-1/2/4/5 的 8\*16、12\*24、16\*32 字型。

- 支持使用者自定义半型字角与全型字 (8\*16、12\*24、16\*32、16\*16、32\*32) 。

- 支持 48\*48、72\*72 大全型字。

- 提供可程序文字光标。

- 支持垂直与水平放大字型 (\*1, \*2, \*3, \*4 倍) 。

- 支持文字 90 度旋转。

## SPI Master 界面

- TFT 图形加速器提供外部串行闪存 (Serial Flash) 数据复制至图框缓冲区。

- 兼容标准 QSPI 规格 NOR/NAND Flash。

- 支持 Nand Flash 坏块处理。

- 支持 MCU 对 SPI Flash 的 by Pass Mode。

- 提供 16bytes 读取 FIFO 及 16bytes 写入 FIFO。

- 在 Tx FIFO 完全清空并且 SPI Tx/Rx 引擎闲置时会发出中断。

- 提供额外 2 组兼容标准 SPI 接口。

## I2C 界面

- MCU 提供 I2C 接口与外部 I2C 装置连接。

- 提供标准传输模式 (100kbps) 与快速传输模式 (400kbps) 。

## PWM 界面

- MCU 提供 8 个 PWM 接口。

- TFT 控制器内建 2 组 16-bits 计数器，提供 2 个 PWM 输出接口。

- 可程序化的工作周期定。

## 中断信号界面

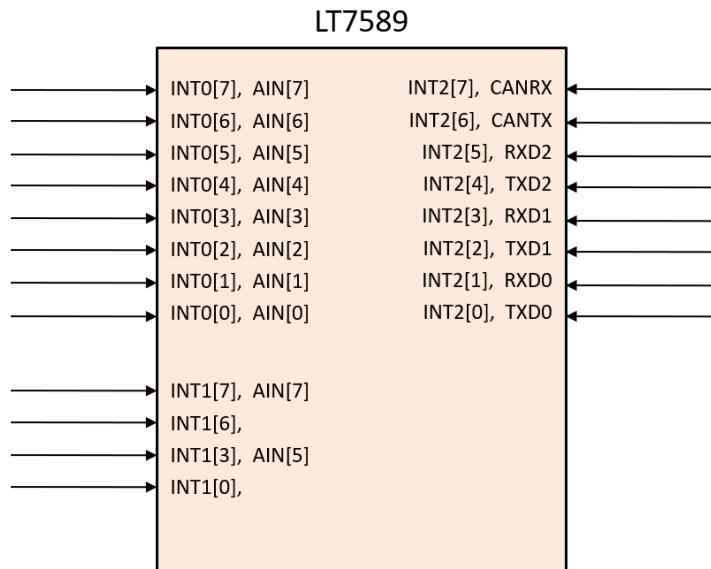

- MCU 最多可提供 19 个中断输入接口。

- TFT 控制器提供 1 中断输出接口。

## GPIO 界面

- MCU 最多可提供 24 个 GPIO 接口。

- TFT 控制器最多可提供 17 个 GPIO 接口。

## 模拟输入界面

- MCU 提供 8 个 ADC 的模拟输入接口。

## 复位方式

- MCU 提供 电源开启复位、外部复位输入、软件复位、看门狗复位和电压侦测复位

- TFT 控制器提供电源启动复位、外部硬件复位和软件命令复位。

## 省电模式

- 提供 3 种省电模式：待机 (Standby) 、休眠 (Suspend) 与睡眠 (Sleep) 模式。

- 支持使用 MCU 唤醒。

## 时钟 (Clock)

- MCU 与 TFT 控制器独立时钟。

- MCU 内建精准高频时钟

- 内建 RTC、外部 32KHz 晶振电路。

- TFT 控制器内建可程序化 PLL，提供内部时钟、外部 LCD 时钟、内部显示内存时钟。

## 电源供应

- VDD 电压: 3.3V +/- 0.3V。

- 内建 1.2V LDO。

## 封装型式

- QFN-96Pin (10\*10mm<sup>2</sup>) 封装。

- LQFP-128Pin (14\*14mm<sup>2</sup>) 封装。

## 工作温度

- -40°C~85°C。(@180MHz)

## 2. 引脚信号

### 2.1. 芯片脚位图

图 2-1: LT7589A 引脚图 (QFN-96Pin)

图 2-2: LT7589B 引脚图 (LQFP-128Pin)

## 2.2. 信号说明

### 2.2.1. SCI (Uart) 串口信号

表 2-1: SCI (Uart) 串口信号

| 脚号<br>LT7589A | 脚号<br>LT7589B | 引脚名称 | I/O | 功 能 说 明                                                                                                    |

|---------------|---------------|------|-----|------------------------------------------------------------------------------------------------------------|

| 37            | 43            | RXD0 | I   | <b>串口通信(Uart) #0 接收数据输入</b><br>此信号用于 SCI #0 接收器数据输入，可用于连接外部 SCI 接口之元件或是模块。也可作为普通的 GPIO 或是中断输入接口 INT2[1]使用。 |

| 36            | 42            | TXD0 | O   | <b>串口通信(Uart) #0 发送数据输出</b><br>此信号用于 SCI #0 发送器数据输出，可用于连接外部 SCI 接口之元件或是模块。也可作为普通的 GPIO 或是中断输入接口 INT2[0]使用。 |

| 39            | 45            | RXD1 | I   | <b>串口通信(Uart) #1 接收数据输入</b><br>此信号用于 SCI #1 接收器数据输入，经由内部 MCU 的寄存器设定，也可作为普通的 GPIO 或是中断输入接口 INT2[3]使用。       |

| 38            | 44            | TXD1 | O   | <b>串口通信(Uart) #1 发送数据输出</b><br>此信号用于 SCI #1 发送器数据输出，经由内部 MCU 的寄存器设定，也可作为普通的 GPIO 或是中断输入接口 INT2[2]使用。       |

| 4             | 7             | RXD2 | I   | <b>串口通信(Uart) #2 接收数据输入</b><br>此信号用于 SCI #2 接收器数据输入，经由内部 MCU 的寄存器设定，也可作为普通的 GPIO 或是中断输入接口 INT2[5]使用。       |

| 92            | 127           | TXD2 | O   | <b>串口通信(Uart) #2 发送数据输出</b><br>此信号用于 SCI #2 发送器数据输出，经由内部 MCU 的寄存器设定，也可作为普通的 GPIO 或是中断输入接口 INT2[4]使用。       |

### 2.2.2. LCD 屏接口信号

表 2-2: LCD 屏接口信号

| 脚号<br>LT7589A             | 脚号<br>LT7589B                | 引脚名称                                | I/O | 功 能 说 明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

|---------------------------|------------------------------|-------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|--|---------|---------|-------|----------|----|-------|----------|----|-------|----------|----|-------|----|----|-------|----|----|-------|----|----|-------|----|----|-------|----|----|-------|----------|----|-------|----------|----|--------|----|----|--------|----|----|--------|----|----|--------|----|----|--------|----|----|--------|----|----|--------|----------|----|--------|----------|----|--------|----------|----|--------|----|----|--------|----|----|--------|----|----|--------|----|----|--------|----|----|

| 86~82,<br>80~72,<br>70~61 | 118~114<br>112~104<br>101~92 | PD[23:19],<br>PD[18:10],<br>PD[9:0] | O   | <p><b>LCD 数据总线</b><br/>输出数据至 TFT-LCD 屏的数据总线，可经由寄存器来设定连接相对应的 RGB 总线。</p> <table border="1"> <thead> <tr> <th rowspan="2">Pin<br/>Name</th> <th colspan="2">TFT-LCD Interface</th> </tr> <tr> <th>16-bits</th> <th>24-bits</th> </tr> </thead> <tbody> <tr><td>PD[0]</td><td>GPIOD[0]</td><td>B0</td></tr> <tr><td>PD[1]</td><td>GPIOD[1]</td><td>B1</td></tr> <tr><td>PD[2]</td><td>GPIOD[6]</td><td>B2</td></tr> <tr><td>PD[3]</td><td>B0</td><td>B3</td></tr> <tr><td>PD[4]</td><td>B1</td><td>B4</td></tr> <tr><td>PD[5]</td><td>B2</td><td>B5</td></tr> <tr><td>PD[6]</td><td>B3</td><td>B6</td></tr> <tr><td>PD[7]</td><td>B4</td><td>B7</td></tr> <tr><td>PD[8]</td><td>GPIOD[2]</td><td>G0</td></tr> <tr><td>PD[9]</td><td>GPIOD[3]</td><td>G1</td></tr> <tr><td>PD[10]</td><td>G0</td><td>G2</td></tr> <tr><td>PD[11]</td><td>G1</td><td>G3</td></tr> <tr><td>PD[12]</td><td>G2</td><td>G4</td></tr> <tr><td>PD[13]</td><td>G3</td><td>G5</td></tr> <tr><td>PD[14]</td><td>G4</td><td>G6</td></tr> <tr><td>PD[15]</td><td>G5</td><td>G7</td></tr> <tr><td>PD[16]</td><td>GPIOD[4]</td><td>R0</td></tr> <tr><td>PD[17]</td><td>GPIOD[5]</td><td>R1</td></tr> <tr><td>PD[18]</td><td>GPIOD[7]</td><td>R2</td></tr> <tr><td>PD[19]</td><td>R0</td><td>R3</td></tr> <tr><td>PD[20]</td><td>R1</td><td>R4</td></tr> <tr><td>PD[21]</td><td>R2</td><td>R5</td></tr> <tr><td>PD[22]</td><td>R3</td><td>R6</td></tr> <tr><td>PD[23]</td><td>R4</td><td>R7</td></tr> </tbody> </table> <p>当 LCD 设置为 16/18bpp 功能模式时，有些 PD 可被定义为 GPIO 引脚。</p> | Pin<br>Name | TFT-LCD Interface |  | 16-bits | 24-bits | PD[0] | GPIOD[0] | B0 | PD[1] | GPIOD[1] | B1 | PD[2] | GPIOD[6] | B2 | PD[3] | B0 | B3 | PD[4] | B1 | B4 | PD[5] | B2 | B5 | PD[6] | B3 | B6 | PD[7] | B4 | B7 | PD[8] | GPIOD[2] | G0 | PD[9] | GPIOD[3] | G1 | PD[10] | G0 | G2 | PD[11] | G1 | G3 | PD[12] | G2 | G4 | PD[13] | G3 | G5 | PD[14] | G4 | G6 | PD[15] | G5 | G7 | PD[16] | GPIOD[4] | R0 | PD[17] | GPIOD[5] | R1 | PD[18] | GPIOD[7] | R2 | PD[19] | R0 | R3 | PD[20] | R1 | R4 | PD[21] | R2 | R5 | PD[22] | R3 | R6 | PD[23] | R4 | R7 |

| Pin<br>Name               | TFT-LCD Interface            |                                     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

|                           | 16-bits                      | 24-bits                             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

| PD[0]                     | GPIOD[0]                     | B0                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

| PD[1]                     | GPIOD[1]                     | B1                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

| PD[2]                     | GPIOD[6]                     | B2                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

| PD[3]                     | B0                           | B3                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

| PD[4]                     | B1                           | B4                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

| PD[5]                     | B2                           | B5                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

| PD[6]                     | B3                           | B6                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

| PD[7]                     | B4                           | B7                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |

| PD[8]                     | GPIOD[2]                     | G0                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                   |  |         |         |       |          |    |       |          |    |       |          |    |       |    |    |       |    |    |       |    |    |       |    |    |       |    |    |       |          |    |       |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |        |          |    |        |          |    |        |          |    |        |    |    |        |    |    |        |    |    |        |    |    |        |    |    |