High Performance Uart TFT Display Controller

# **Brief Specification**

V1.2

<u>www.levetop.cn</u> Levetop Semiconductor Co., Ltd.

| Version | Release Date | Description                                                                                                                                                       |

|---------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0    | 2024/10/29   | <ul> <li>LT7589 Preliminary Release</li> </ul>                                                                                                                    |

| V1.0A   | 2024/12/30   | <ul> <li>Update Application Circuit</li> </ul>                                                                                                                    |

| V1.1    | 2025/03/20   | <ul> <li>Update Pin - VDD33_IO Description</li> <li>Update Application Circuit</li> </ul>                                                                         |

| V1.2    | 2025/04/21   | <ul> <li>Modify the pin signal description of "LCD_XI"</li> <li>Update Table 6-4 External Flash Signal Description</li> <li>Update Application Circuit</li> </ul> |

## Version History

## **Copyright**

The copyright of this document belongs to Levetop Semiconductor Co., Ltd. If you need to copy or duplicate it, please obtain Levetop Semiconductor's permission in advance. Although the information recorded in this document has been proofread, Levetop Semiconductor assumes no responsibility for the specifications of the document usage instructions. The applications mentioned in the document are for reference only, and Levetop Semiconductor does not guarantee that such applications do not require further modification. Levetop Semiconductor reserves the right to change its product specifications or documents without prior notice. For the latest product information, please visit our website Https://www.levetop.cn.

## **Content**

| Ve  | rsior | History                                | 2   |

|-----|-------|----------------------------------------|-----|

| Со  | pyric | Jht                                    | 2   |

| Со  | nten  | t                                      | 3   |

| Fig | jure  | List                                   | 4   |

| Та  | ble L | ist                                    | 4   |

| 1.  |       | Introduction                           |     |

| 2.  |       | lication Block Diagram                 |     |

| 3.  | Inte  | nal Block Diagram                      | 7   |

| 4.  | Fea   | tures                                  | 8   |

| 5.  |       | Assignment                             |     |

| 6.  | Pin   | Description                            | 12  |

| -   | 6.1   | SCI (Uart) Signals                     | .12 |

|     | 6.2   | LCD Panel Signals                      | .13 |

|     | 6.3   | QSPI Signals                           | .14 |

|     | 6.4   | External Flash Signals                 |     |

|     | 6.5   | PWM Signals                            | .16 |

|     | 6.6   | USB Signals                            | .18 |

|     | 6.7   | GPIO and Intrrrupt Signals             | .18 |

|     | 6.8   | ADC Input Signals                      | .20 |

|     | 6.9   | Miscellaneous Signals                  | .20 |

|     | 6.10  | Power and Clock Signals                |     |

|     | 6.11  | GPIO Resources of Different TFT Panels | .24 |

| 7.  | Fun   | ction Description                      | 26  |

| 8.  | Pac   | kage Information                       | 28  |

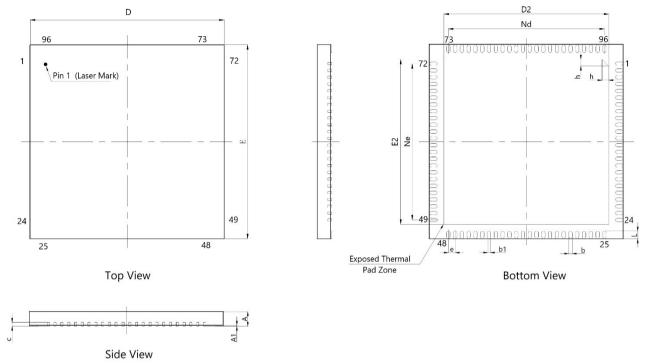

|     | 8.1   | LT7589A (QFN-96pin)                    |     |

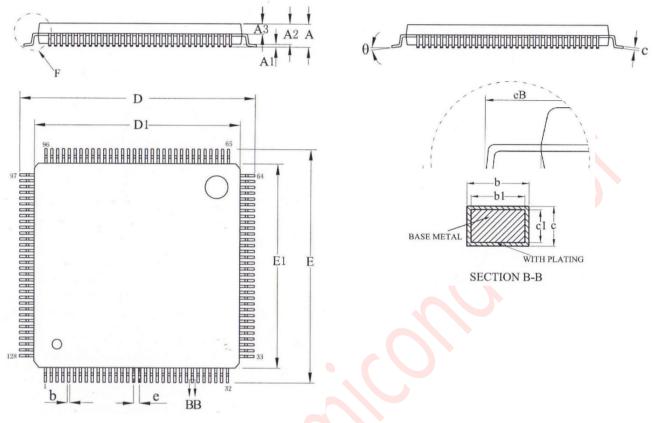

|     | 8.2   | LT7589B (LQFP-128pin)                  |     |

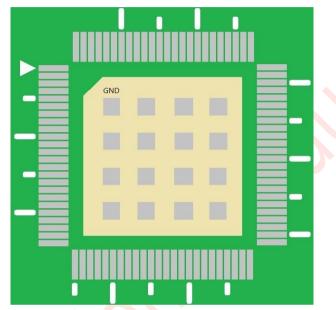

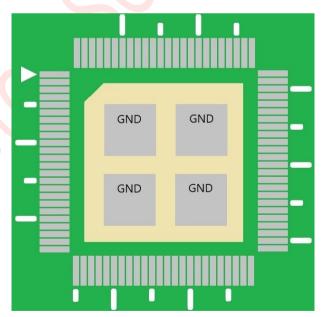

|     | 8.3   | LT7589A PCB Layout Suggestions         | .30 |

| 9.  | Арр   | lication Circuit                       | 31  |

## Figure List

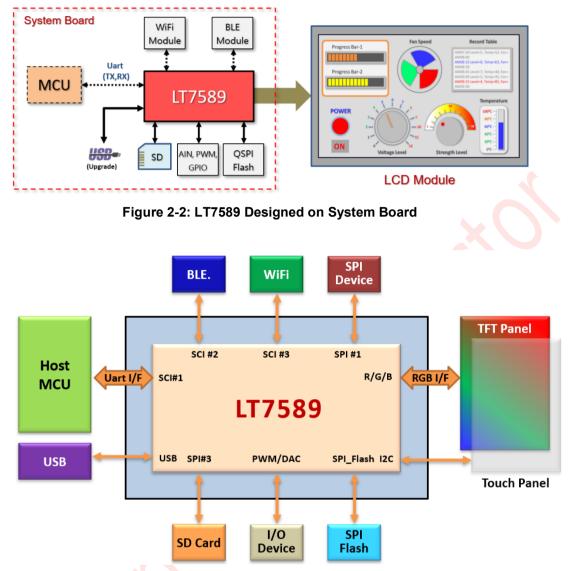

| Figure 2-1: LT7589 Designned on TFT Module                                              | 5  |

|-----------------------------------------------------------------------------------------|----|

| Figure 2-2: LT7589 Designned on System Board                                            | 6  |

| Figure 2-3: LT7589 Application Architecture                                             | 6  |

| Figure 3-1: LT7589 Internal Block Diagram                                               | 7  |

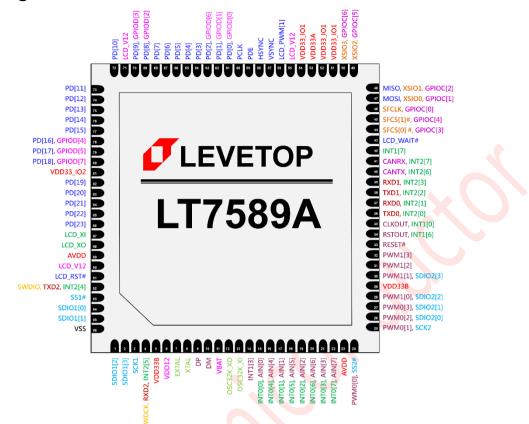

| Figure 5-1: LT7589A Pin Assignment (QFN-96Pin)                                          | 10 |

| Figure 5-2: LT7589B Pin Assignment (LQFP-128Pin)                                        | 11 |

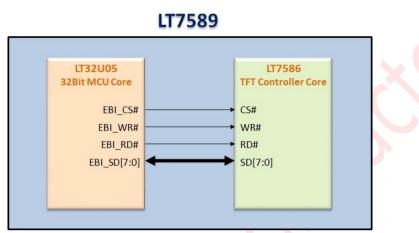

| Figure 7-1: Communication Mode between LT7589 Internal MCU and TFT Graphics Accelerator | 26 |

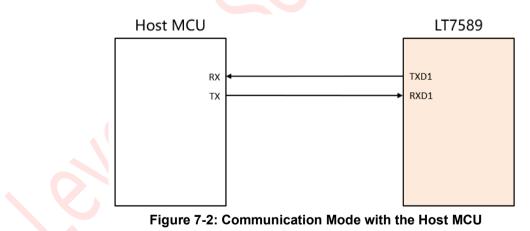

| Figure 7-2: Communication Mode with the Host MCU                                        | 26 |

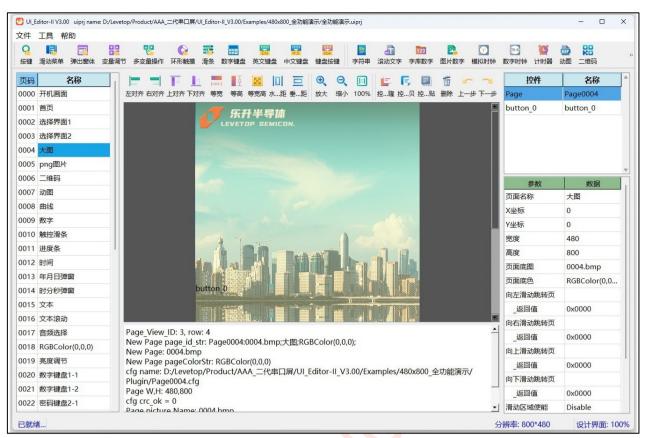

| Figure 7-3: The Main Screen of UI_Editor Tool                                           | 27 |

| Figure 7-4: LT7589 Internal Memory                                                      | 27 |

| Figure 8-1: QFN-96Pin Outline                                                           | 28 |

| Figure 8-2: LQFP-128Pin Outline                                                         |    |

| Figure 8-3: Design Suggestion-1 for LT7589A Bottom Pad PCB Layout                       | 30 |

| Figure 8-4: Design Suggestion-2 for LT7589A Bottom Pad PCB Layout                       | 30 |

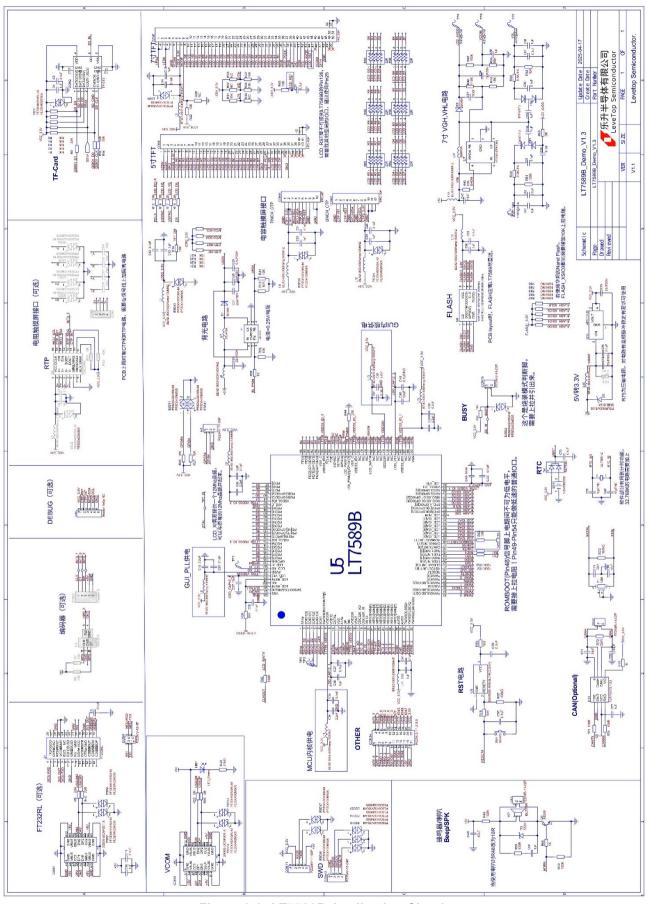

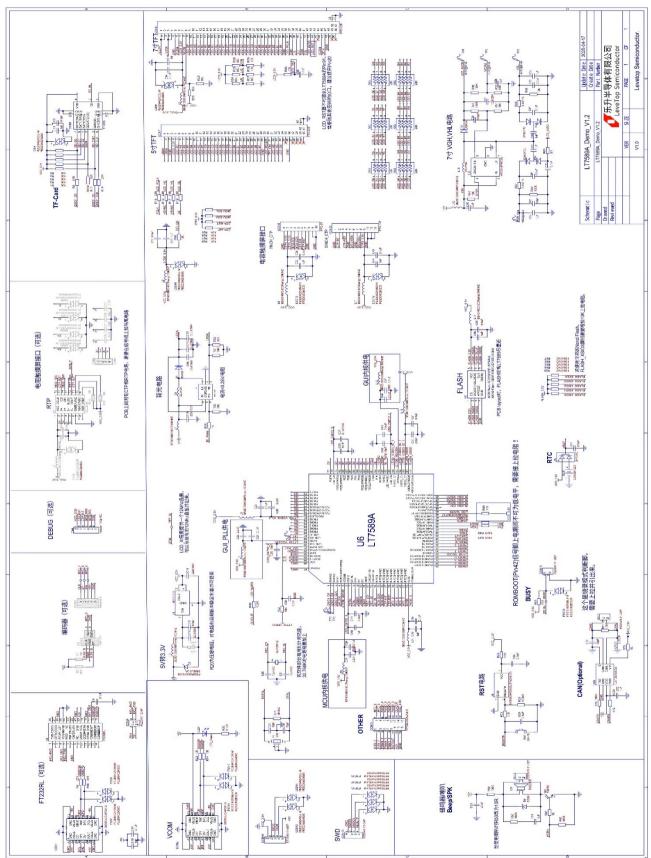

| Figure 9-1: LT7589A Application Circuit                                                 | 31 |

| Figure 9-2: LT7589B Application Circuit                                                 | 32 |

## Table List

| Table 3-1: Part Number                | 7  |

|---------------------------------------|----|

| Table 6-1: SCI (Uart) Signals         | 12 |

| Table 6-2: LCD Panel Signals          | 13 |

| Table 6-3: QSPI Signals               | 14 |

| Table 6-4: External Flash Signals     | 15 |

| Table 6-5: PWM Signals                | 16 |

| Table 6-6: USB Signals                | 18 |

| Table 6-7: GPIO and Interrupt Signals | 18 |

| Table 6-8: ADC Input Signals          | 20 |

| Table 6-9: Miscellaneous Signals      | 20 |

| Table 6-10: Power and Clock Signals   |    |

| Table 6-11: LT7589A GPIO Resources    | 24 |

| Table 6-12: LT7589B GPIO Resources    | 25 |

| Table 8-1: QFN-96Pin Dimensions       |    |

| Table 8-2: LQFP-128Pin Dimensions     | 29 |

|                                       |    |

## 1. Chip Introduction

LT7589 is a high-performance Serial Uart TFT Panel Controller. Internally integrated with a 32-bit RISC MCU and a GUI (Graphic User Interface) with TFT LCD graphics display controller, the main function is to provide Uart serial communication, allowing the main control MCU to easily present the information to be displayed on the TFT panel through simple serial commands. The internal hardware of LT7589 also provides JPG image decoding PIP (Picture-in-Picture), Geometric drawing and other functions can improve the display efficiency of TFT panel and reduce the time required for MCU to process graphic displays. The LT7589 supports display resolutions ranging from 480 \* 480 (QVGA) to 1280 \* 800, suitable for 16/24bit RGB interface TFT displays.

The internal MCU of LT7589 has a maximum clock frequency of 200MHz, contains 2MB Flash, 768KB SRAM, 16MB display memory, and is combined with JPG decoder, 2D

graphics acceleration display, DMA data reading, and high-speed QSPI Flash interface to quickly read images, animations, word libraries, and other information stored in external QSPI Flash, with good display performance. LT7589 can be used in conjunction with UI editing software (UI-Editor) and simulation software (UI-Emulator) developed by Levetop Semiconductor to directly import and develop display interfaces for designed UI materials and display interaction logic on a computer. Its supported display functions include image display, animation display, sliding menu display, progress bar display, string display, Chinese English keyboard, numeric keyboard, analog clock, digital clock, pointer display, QR code generation, multi language, audio playback, variable control, and control effects combined with touch screen or encoder functions. In addition to the serial port screen Uart communication interface, LT7589 also provides multiple sets of SCI (Uart) interfaces to connect components such as Bluetooth modules, WiFi modules, etc. It also offers CanBus, SD card (SPI mode), analog input AIN, PWM, and INT interrupt interfaces, and comes with an RTC clock. It can also be used for GUI graphic development in Little VGL, with good fluency and high cost-effectiveness.

Due to its high capacity of Flash and SRAM, the LT7589 can also be used as a main control MCU with a TFT controller, completing the main control and TFT display functions with one LT7589. Its display function is very suitable for electronic products with TFT-LCD panels below 1280x800 resolution, or to replace the original monochrome panel products, enhancing the product's intelligent display of information, increasing product quality and grade. The powerful display function of LT7589 is very suitable for use in electronic products with TFT-LCD panels, such as various smart home appliances, car dashboards, motorcycle panels, multifunctional transaction machines, industrial controls, electronic instruments, medical beauty equipment, testing equipment, charging equipment, inverters, UPS and other power equipment, audio equipment, as well as smart speakers with TFT panel, robots and other products.

#### 2. Application Block Diagram WiFi BLE Module Module Main System Uart Progress Bar-2 (TX,RX) MCU LT7589 B QSPI SD (Upgrade) Flash (Ungrade) LCD Module

Figure 2-1: LT7589 Designed on TFT Module

Figure 2-3: LT7589 Application Architecture

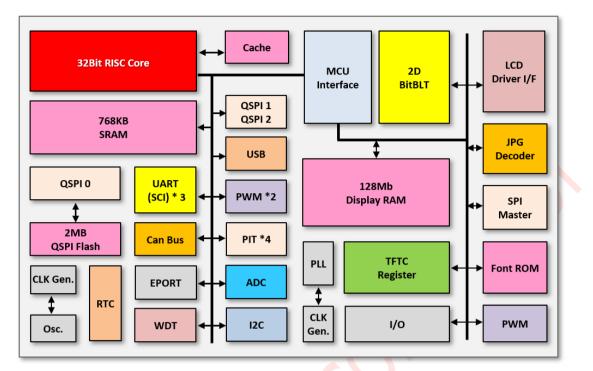

## 3. Internal Block Diagram

Figure 3-1: LT7589 Internal Block Diagram

Table 3-1: Part Number

| Model   | Package  | Display RAM | Resolution | Colors                      |

|---------|----------|-------------|------------|-----------------------------|

| LT7589A | QFN-96   | 128Mb       | 1280*800   | 16.7M Color<br>αRGB 8:8:8:8 |

| LT7589B | LQFP-128 | 128Mb       | 1280*800   | 16.7M Color<br>αRGB 8:8:8:8 |

## **7** LT7589

## 4. Features

#### **Host MCU Interface**

- Support Uart, USB Interface

- Embedded 32Bit MCU, main clock is 180MHz, and 200MHz for max.

#### **USB Interface**

Support USB2.0 Full Speed.

#### SCI (Uart) Interface

- Supports Three SCI (Serial Communications Interface)

- Components or modules that can be connected to external SCI interfaces

#### Memory

- MCU Embedded 2M bytes Flash

- MCU Embedded 512K+256K bytes SRAM

- TFT Controller Embedded 128Mbit Display RAM

#### **Display Data Format**

- 16bpp: Color RGB 5:6:5 (2bytes/pixel)

- 24bpp: Color RGB 8:8:8 (3bytes/pixel)

- αRGB 4:4:4:4 (4,096 Index color/pixel, including transparency attribute)

- 32bpp : Color αRGB 8:8:8:8 (4bytes/pixel)

#### Panel Interface and Resolution

- Supports 16 or 24bits RGB Interface Panel

- Supported resolutions for bare metal development:

- VGA : 640\*480 TFT Panel

- WVGA : 800\*480 TFT Panel

- SVGA : 800\*600 TFT Panel

- > XGA : 1024\*768 TFT Panel

- > SXGA : 1280\*1024 TFT Panel

- Maximum resolution supported during serial TFT panel development: 1280\*800

#### **Geometry Display accelerator**

Provide drawing functions such as drawing points, lines, curves, ellipses, triangles, rectangles, rounded rectangles, etc

#### **Display Functions**

- Built in JPG hardware decoder

- Support users to define four 32\*32 graphic cursor options.

- Provide virtual display function: Virtual display can display images larger than the size of the LCD panel, so that the images can easily scroll in any direction.

- Provide Picture in Picture (PIP) display: Supports two PIP window regions: the enabled PIP window is displayed above the main window, while the PIP1 window is displayed above the PIP2 window.

- Support multiple display functions: You can switch the main display window between display buffers to achieve simple animation display effects.

- Support the function of quickly displaying images when awakened.

- Supports mirroring and vertical flipping display functions.

- Color Bar Display: It can still be displayed in ribbon format without writing data to the internal display memory, with a default resolution of 640 \* 480 pixels.

#### **BitBLT Engine**

- Built in 2D BitBLT engine.

- Provide the function of copying images with raster operation.

- Provide color depth conversion.

- Solid filling and pattern filling functions:

- Provide user-defined 8\*8 images or 16\*16 images.

- Provide the function of combining two images into one image:

- Chroma Keying function: Mix the image with specified RGB colors based on transparency

- Window Alpha blending mode: Mix two images based on the transparency within the specified area.

- Pixel blending transparency mode (Dot Alpha blending): Mix two images based on RGB format and transparency.

**T**LT7589

#### **Display Text Mode**

- Built in ISO/IEC 8859-1/2/4/5 font sizes of 8\*16, 12\*24, and 16\*32

- Support users to customize half shaped character angles and full shaped characters (8\*16, 12\*24, 16\*32, 16\*16, 32\*32).

- Supports full font sizes of 48\*48 and 72\*72

- Provide programmable text cursor.

- Supports vertical and horizontal font enlargement (\*1, \*2, \*3, \*4x).

- Supports 90 degree rotation of text

#### **SPI Master Interface**

- The TFT graphics accelerator provides external serial flash data copying to the frame buffer.

- Compatible with standard QSPI specifications NOR/NAND Flash.

- Support bad block handling in Nand Flash.

- Support MCU to use Pass Mode for SPI Flash.

- Provide 16 bytes read FIFO and 16 bytes write FIFO.

- When the Tx FIFO is completely cleared and the SPI Tx/Rx engine is idle, an interrupt will be issued.

- Provide 2 additional sets of compatible standard SPI interfaces.

#### **I2C Interface**

- MCU provides I2C interface to connect with external I2C devices

- Provide standard transmission mode (100kbps) and fast transmission mode (400kbps)

#### **PWM Interface**

- MCU provides 8 PWM interfaces

- The TFT controller has two built-in 16bit counters and provides two PWM output interfaces

- Programmable operation cycle

#### Interrupt Signals

- MCU can provide up to 19 interrupt input

- The TFT controller provides an interrupt output interface.

#### GPIO

- MCU can provide up to 24 GPIO Port

- The TFT controller can provide up to 17 GPIO Port

#### Analog Input

MCU Supports eight ADC Analog Input

#### Reset

- MCU provides power on reset, external reset input, software reset, watchdog reset, and voltage detection reset

- The TFT controller provides power on reset, external hardware reset, and software command reset

#### Power Saving Mode

- Support Standby mode, Suspend mode and Sleep Mode

- Support MCU wake up

#### Clock

- MCU and TFT controller have independent clocks.

- MCU built-in precise high-frequency clock

- Built in RTC and external 32KHz crystal oscillator circuit.

- TFT controller with built-in programmable PLL, providing internal clock, external LCD clock, and internal display memory clock

#### **Power Supply**

- VDD Power: 3.3V +/- 0.3V

- Embedded 1.2V LDO

#### Package Type

- QFN-96Pin (10\*10mm<sup>2</sup>)

- LQFP-128Pin (14\*14mm<sup>2</sup>)

#### **Operation Temp.**

■ -40°C~85°C。(@180MHz)

**T**LT7589

## 5. Pin Assignment

#### Figure 5-1: LT7589A Pin Assignment (QFN-96Pin)

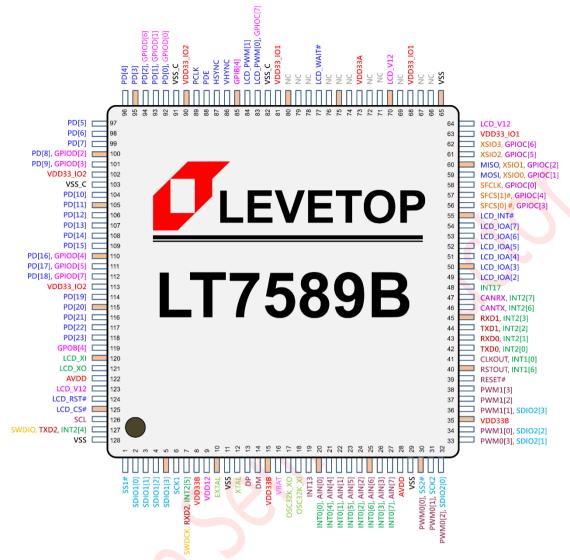

Figure 5-2: LT7589B Pin Assignment (LQFP-128Pin)

## 6. Pin Description

## 6.1 SCI (Uart) Signals

#### Table 6-1: SCI (Uart) Signals

| <b>Pin #</b><br>LT7589A | Pin #<br>LT7589B | Pin Name | I/O | Description                                                                                                                                                                                                          |

|-------------------------|------------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                  |          |     | Serial Communication (Uart) #0 Receives Data Input                                                                                                                                                                   |

| 37                      | 43               | RXD0     | Ι   | This signal is used for SCI #0 receiver data input and can be<br>used to connect external SCI interface components or<br>modules. It can also be used as a regular GPIO or interrupt<br>input interface INT2[1].     |

|                         |                  |          |     | Serial communication (Uart) #0 Transmission Data Output                                                                                                                                                              |

| 36                      | 42               | TXD0     | 0   | This signal is used for SCI #0 transmitter data output and can<br>be used to connect external SCI interface components or<br>modules. It can also be used as a regular GPIO or interrupt<br>input interface INT2[0]. |

|                         |                  |          |     | Serial Communication (Uart) #1 Receives Data Input                                                                                                                                                                   |

| 39                      | 45               | RXD1     | I   | This signal is used for SCI #1 receiver data input and can be<br>used to connect external SCI interface components or<br>modules. It can also be used as a regular GPIO or interrupt<br>input interface INT2[3].     |

|                         |                  |          |     | Serial communication (Uart) #1 Transmission Data Output                                                                                                                                                              |

| 38                      | 44               | TXD1     | 0   | This signal is used for SCI #1 transmitter data output and can<br>be used to connect external SCI interface components or<br>modules. It can also be used as a regular GPIO or interrupt<br>input interface INT2[2]. |

|                         |                  |          |     | Serial Communication (Uart) #2 Receives Data Input                                                                                                                                                                   |

| 4                       | 7                | RXD2     | _   | This signal is used for SCI #2 receiver data input and can be<br>used to connect external SCI interface components or<br>modules. It can also be used as a regular GPIO or interrupt<br>input interface INT2[5].     |

|                         |                  |          |     | Serial communication (Uart) #2 Transmission Data Output                                                                                                                                                              |

| 92                      | 127              | TXD2     | 0   | This signal is used for SCI #2 transmitter data output and can<br>be used to connect external SCI interface components or<br>modules. It can also be used as a regular GPIO or interrupt<br>input interface INT2[4]. |

|                         | Ŝ.               |          |     |                                                                                                                                                                                                                      |

## 6.2 LCD Panel Signals

| Pin #<br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name     | I/O |      |                                                          | Description         |                      |       |

|------------------|-------------------------|--------------|-----|------|----------------------------------------------------------|---------------------|----------------------|-------|

|                  |                         |              |     | TFT  | Panel Data Bus<br>LCD data bus outț<br>rresponding RGB l |                     |                      | nnect |

|                  |                         |              |     |      | Pin                                                      | TFT-LCD             | Interface            |       |

|                  |                         |              |     |      | Name                                                     | 16bits              | 24bits               |       |

|                  |                         |              |     |      | PD[0]                                                    | GPIOD[0]            | B0                   |       |

|                  |                         |              |     |      | PD[1]                                                    | GPIOD[1]            | B1                   |       |

|                  |                         |              |     |      | PD[2]                                                    | GPIOD[6]            | B2                   |       |

|                  |                         |              |     |      | PD[3]                                                    | B0                  | B3                   |       |

|                  |                         |              |     |      | PD[4]                                                    | B1                  | B4                   |       |

|                  |                         |              |     |      | PD[5]                                                    | B2                  | B5                   |       |

|                  |                         |              |     |      | PD[6]                                                    | B3                  | B6                   |       |

|                  |                         |              |     |      | PD[7]                                                    | B4                  | B7                   |       |

|                  |                         |              |     |      | PD[8]                                                    | GPIOD[2]            | G0                   |       |

| 86~82,           | 118~114,                | PD[23:19],   | о   |      | PD[9]                                                    | GPIOD[3]            | G1                   |       |

| 80~72,           | 112~104,                | PD[18:10],   |     |      | PD[10]                                                   | G0                  | G2                   |       |

| 70~61            | 101~92                  | PD[9:0]      |     |      | PD[11]                                                   | G1                  | G3                   |       |

|                  |                         |              |     |      | PD[12]                                                   | G2                  | G4                   |       |

|                  |                         |              |     |      | PD[13]                                                   | G3                  | G5                   |       |

|                  |                         |              |     |      | PD[14]                                                   | G4                  | G6                   |       |

|                  |                         |              |     |      | PD[15]                                                   | G5                  | G7                   |       |

|                  |                         | $\mathbf{X}$ |     |      | PD[16]                                                   | GPIOD[4]            | R0                   |       |

|                  |                         |              |     |      | PD[17]                                                   | GPIOD[5]            | R1                   |       |

|                  |                         |              |     |      | PD[18]                                                   | GPIOD[7]            | R2                   |       |

|                  |                         |              |     |      | PD[19]                                                   | R0                  | R3                   |       |

|                  |                         |              |     |      | PD[20]                                                   | R1                  | R4                   |       |

|                  |                         |              |     |      | PD[21]                                                   | R2                  | R5                   |       |

|                  |                         |              |     |      | PD[22]                                                   | R3                  | R6                   |       |

|                  |                         |              |     |      | PD[23]                                                   | R4                  | R7                   |       |

|                  |                         |              |     |      | n the LCD is set t<br>be defined as GPIC                 |                     | tion mode, some      | PDs   |

|                  |                         |              |     | Pixe | Clock                                                    |                     |                      |       |

| 60               | 89                      | PCLK         | 0   | Gene | eric TFT interface s<br>internal PLL.                    | signal for panel so | can clock. It derive | es    |

| <b>Pin #</b><br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name | I/O | Description                                                                                 |

|-------------------------|-------------------------|----------|-----|---------------------------------------------------------------------------------------------|

| 57                      | 86                      | VSYNC    | 0   | <b>VSYNC Pulse Signal</b><br>Generic TFT interface signal for vertical synchronous pulse.   |

| 58                      | 87                      | HSYNC    | 0   | <b>HSYNC Pulse Signal</b><br>Generic TFT interface signal for horizontal synchronous pulse. |

| 59                      | 88                      | PDE      | 0   | Data Enable Signal<br>Generic TFT interface signal for data valid or data enable.           |

## 6.3 QSPI Signals

#### Table 6-3: QSPI Signals

| Pin #<br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name           | I/O | Description                                                                                                                                       |

|------------------|-------------------------|--------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                         |                    |     | QSPI #1 Serial Clock Signal                                                                                                                       |

| 3                | 6                       | SCK1               | 0   | This signal is the clock signal output of the first group SPI and<br>can be used to connect components or modules of external<br>SPI interfaces.  |

| 93               | 1                       | SS1#               | 0   | QSPI #1 Chip Selection Signal                                                                                                                     |

| 30               | I                       | 001#               | 0   | This signal is the chip selection output of the first group SPI.                                                                                  |

|                  |                         |                    |     | Data Output/Input Signal of QSPI #1                                                                                                               |

| 94               | 2                       | SDIO1[0]           | 10  | This signal is the output/input signal of the first group QSPI data 0.                                                                            |

|                  |                         |                    | Ю   | Data Output/Input Signal of QSPI #1                                                                                                               |

| 95               | 3                       | SDIO1[1]           |     | This signal is the output/input signal of the first group QSPI data 1.                                                                            |

|                  |                         |                    |     | Data Output/Input Signal of QSPI #1                                                                                                               |

| 1                | 4                       | SDIO1[2]           | 10  | This signal is the output/input signal of the first group QSPI data 2.                                                                            |

|                  |                         |                    |     | Data Output/Input Signal of QSPI #1                                                                                                               |

| 2                | 5                       | SDIO1[3]           | IO  | This signal is the output/input signal of the first group QSPI data 3.                                                                            |

|                  |                         |                    |     | QSPI #2 Serial Clock Signal                                                                                                                       |

| 25               | 31                      | SCK2<br>PWM0[1]    | 0   | This signal is the clock signal output of the second group SPI<br>and can be used to connect components or modules of<br>external SPI interfaces. |

|                  |                         |                    |     | This pin shares with pin PWM0[1].                                                                                                                 |

|                  |                         | 000/               |     | QSPI #2 Chip Selection Signal                                                                                                                     |

| 24               | 30                      | 30 SS2#<br>PWM0[0] | 0   | This signal is the chip selection output of the second group SPI.                                                                                 |

|                  |                         |                    |     | This pin shares with pin PWM0[0].                                                                                                                 |

| Pin #<br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name            | I/O | Description                                                             |

|------------------|-------------------------|---------------------|-----|-------------------------------------------------------------------------|

|                  |                         |                     |     | Data Output/Input Signal of QSPI #2                                     |

| 26               | 32                      | SDIO2[0]<br>PWM0[2] | Ю   | This signal is the output/input signal of the second group QSPI data 0. |

|                  |                         |                     |     | This pin shares with pin PWM0[2].                                       |

|                  |                         |                     |     | Data Output/Input Signal of QSPI #2                                     |

| 27               | 33                      | SDIO2[1]<br>PWM0[3] | Ю   | This signal is the output/input signal of the second group QSPI data 1. |

|                  |                         |                     |     | This pin shares with pin PWM0[3].                                       |

|                  |                         |                     | ю   | Data Output/Input Signal of QSPI #2                                     |

| 28               | 34                      | SDIO2[2]<br>PWM1[0] |     | This signal is the output/input signal of the second group QSPI data 2. |

|                  |                         |                     |     | This pin shares with pin PWM1[0].                                       |

|                  |                         |                     |     | Data Output/Input Signal of QSPI #2                                     |

| 30               | 36                      | SDIO2[3]<br>PWM1[1] | Ю   | This signal is the output/input signal of the second group QSPI data 3. |

|                  |                         |                     |     | This pin shares with pin PWM1[1].                                       |

### 6.4 External Flash Signals

#### Table 6-4: External Flash Signals

| Pin #<br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name             | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|-------------------------|----------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45               | 57                      | SFCS[1]#<br>GPIOC[4] | 10  | External Serial Flash #1 Chip Selection Signal<br>This signal is controlled by the LCD controller inside LT7589. If<br>the serial QSPI function is disabled, this pin can be set to<br>GPOC[4], which defaults to input function.<br>Note:<br>Under the serial panel function framework of Levetop<br>Semiconductor, only SFCS[1]# is allowed to be used as the chip<br>selection signal for external QSPI Flash, and SFCS[0]# cannot<br>be used.                                                                |

| 44               | 56                      | SFCS[0]#<br>GPIOC[3] | Ю   | External Serial Flash #0 Chip Selection Signal<br>This signal is controlled by the LCD controller inside LT7589. If<br>the serial QSPI function is disabled, this pin can be set to<br>GPOC[3], which defaults to input function.<br>Note:<br>Under the serial panel function framework of Levetop<br>Semiconductor, this signal cannot be used as the chip selection<br>signal for external QSPI Flash, and SFCS[1]# must be used.<br>SFCS[0]# can only be used when the customer develops it with<br>own code. |

| Pin #<br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name          | I/O | Description                                                                                                                                          |

|------------------|-------------------------|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                         |                   |     | External Serial Flash Clock Signal                                                                                                                   |

| 46               | 58                      | SFCLK<br>GPIOC[0] | IO  | This pin is a serial clock signal output, controlled by the LCD controller inside LT7589, and connected to external Serial Flash or QSPI components. |

|                  |                         |                   |     | If the serial QSPI function is disabled, this pin can be set to GPOC[0] and default to input function.                                               |

|                  |                         |                   |     | QSPI Data Input/Output Signal 0                                                                                                                      |

| 47               | 59                      | XSIO0<br>GPIOC[1] | IO  | This signal is controlled by the LCD controller inside LT7589,<br>and this data line is connected to an external Serial Flash or<br>QSPI component.  |

|                  |                         |                   |     | If the serial SPI function is disabled, this pin can be set to GPOC[1] and default to input function.                                                |

|                  |                         |                   |     | QSPI Data Input/Output Signal 1                                                                                                                      |

| 48               | 60                      | XSIO1<br>GPIOC[2] | IO  | This signal is controlled by the LCD controller inside LT7589,<br>and this data line is connected to an external Serial Flash or<br>QSPI component.  |

|                  |                         |                   |     | If the serial SPI function is disabled, this pin can be set to GPOC[2] and default to input function.                                                |

|                  |                         |                   |     | QSPI Data Input/Output Signal 2                                                                                                                      |

| 49               | 61                      | XSIO2<br>GPIOC[5] | Ю   | This signal is controlled by the LCD controller inside LT7589,<br>and this data line is connected to an external Serial Flash or<br>QSPI component.  |

|                  |                         |                   |     | If the serial SPI function is disabled, this pin can be set to GPOC[5] and default to input function.                                                |

|                  |                         |                   |     | QSPI Data Input/Output Signal 3                                                                                                                      |

| 50               | 62                      | XSIO3<br>GPIOC[6] | 10  | This signal is controlled by the LCD controller inside LT7589,<br>and this data line is connected to an external Serial Flash or<br>QSPI component.  |

|                  |                         | XO                |     | If the serial SPI function is disabled, this pin can be set to GPOC[6] and default to input function.                                                |

## 6.5 PWM Signals

#### Table 6-5: PWM Signals

|                  |                  | Table 6-5: PWM Signals |     |                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|------------------|------------------|------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin #<br>LT7589A | Pin #<br>LT7589B | Pin Name               | I/O | Description                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                  | 83               | LCD_PWM[0]<br>GPIOC[7] | Ю   | <b>LCD PWM#0 Output Signal</b><br>This signal is controlled by the register of the LCD controller<br>inside LT7589, and is a programmable PWM output signal that<br>can be used to control the backlight or other components of the<br>TFT LCD screen. The output mode of LCD_PWM can be set<br>through the registers of the LCD controller.<br>This pin shares with pin GPOC[7]. |  |  |

| <b>Pin #</b><br>LT7589A | <b>Pin #</b><br>LT7589B  | Pin Name            | I/O | Description                                                                                                                                                                                                                                                                                        |

|-------------------------|--------------------------|---------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                          |                     |     | LCD PWM#1 Output Signal                                                                                                                                                                                                                                                                            |

| 56                      | 84                       | LCD_PWM[1]          | Ю   | This signal is controlled by the register of the LCD controller inside LT7589, and is a programmable PWM output signal that can be used to control the backlight or other components of the TFT LCD screen. The output mode of LCD_PWM [1] can be set through the registers of the LCD controller. |

|                         |                          |                     |     | The PWM0[0] Output Signal Controlled by MCU                                                                                                                                                                                                                                                        |

| 24                      | 30                       | PWM0[0]<br>SS2#     | Ю   | Can be used as PWM output or GPIO, set by internal MCU registers.                                                                                                                                                                                                                                  |

|                         |                          |                     |     | This pin shares with pin SS2#.                                                                                                                                                                                                                                                                     |

|                         |                          |                     |     | The PWM0[1] Output Signal Controlled by MCU                                                                                                                                                                                                                                                        |

| 25                      | 31                       | PWM0[1]<br>SCK2     | ю   | Can be used as PWM output or GPIO, set by internal MCU registers.                                                                                                                                                                                                                                  |

|                         |                          |                     |     | This pin shares with pin SCK2.                                                                                                                                                                                                                                                                     |

|                         |                          |                     | ю   | The PWM0[2] Output Signal Controlled by MCU                                                                                                                                                                                                                                                        |

| 26                      | 5 32 PWM0[2]<br>SDI02[0] |                     |     | Can be used as PWM output or GPIO, set by internal MCU registers.                                                                                                                                                                                                                                  |

|                         |                          |                     |     | This pin share <mark>s</mark> with pin SDIO2[0].                                                                                                                                                                                                                                                   |

|                         |                          |                     |     | The PWM0[3] Output Signal Controlled by MCU                                                                                                                                                                                                                                                        |

| 27                      | 33                       | PWM0[3]<br>SDIO2[1] | Ю   | Can be used as PWM output or GPIO, set by internal MCU registers.                                                                                                                                                                                                                                  |

|                         |                          |                     |     | This pin shares with pin SDIO2[1].                                                                                                                                                                                                                                                                 |

|                         |                          |                     |     | The PWM1[0] Output Signal Controlled by MCU                                                                                                                                                                                                                                                        |

| 28                      | 34                       | PWM1[0]<br>SDIO2[2] | 10  | Can be used as PWM output or GPIO, set by internal MCU registers.                                                                                                                                                                                                                                  |

|                         |                          |                     |     | This pin shares with pin SDIO2[2].                                                                                                                                                                                                                                                                 |

|                         |                          |                     |     | The PWM1[1] Output Signal Controlled by MCU                                                                                                                                                                                                                                                        |

| 30                      | 36                       | PWM1[1]<br>SDIO2[3] | 10  | Can be used as PWM output or GPIO, set by internal MCU registers.                                                                                                                                                                                                                                  |

|                         |                          |                     |     | This pin shares with pin SDIO2[3].                                                                                                                                                                                                                                                                 |

|                         |                          |                     | 10  | The PWM1[2] Output Signal Controlled by MCU                                                                                                                                                                                                                                                        |

| 31                      | 37                       | • PWM1[2]           | IO  | Can be used as PWM output or GPIO, set by internal MCU registers.                                                                                                                                                                                                                                  |

|                         |                          |                     |     | The PWM1[3] Output Signal Controlled by MCU                                                                                                                                                                                                                                                        |

| 32                      | 38                       | PWM1[3]             | Ю   | Can be used as PWM output or GPIO, set by internal MCU registers.                                                                                                                                                                                                                                  |

### 6.6 USB Signals

| Pin #<br>LT7589A | Pin #<br>LT7589B | Pin Name | I/O | Description                                                                    |

|------------------|------------------|----------|-----|--------------------------------------------------------------------------------|

| 9                | 13               | DP       | IO  | <b>USB Data Port (Positive)</b><br>This is the signal of USB data terminal DP. |

| 10               | 14               | DM       | Ю   | USB Data Port (Negative)<br>This is the signal of USB data terminal DM.        |

## Table 6-6: USB Signals

## 6.7 GPIO and Interrupt Signals

#### Table 6-7: GPIO and Interrupt Signals

| Pin #<br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name        | I/O | Description                                                     |

|------------------|-------------------------|-----------------|-----|-----------------------------------------------------------------|

| 15               | 20                      | INT0[0]         | I   | Interrupt INT0[0] Signal                                        |

|                  |                         | AIN[0]          |     | Can be used as an interrupt input or as an analog signal input. |

| 17               | 22                      | INT0[1]         | I   | Interrupt INT0[1] Signal                                        |

|                  |                         | AIN[1]          |     | Can be used as an interrupt input or as an analog signal input. |

| 19               | 24                      | INT0[2]         | I   | Interrupt INT0[2] Signal                                        |

|                  |                         | AIN[2]          | -   | Can be used as an interrupt input or as an analog signal input. |

| 21               | 26                      | INT0[3]         |     | Interrupt INT0[3] Signal                                        |

|                  |                         | AIN[3]          |     | Can be used as an interrupt input or as an analog signal input. |

| 16               | 21                      | INT0[4]         |     | Interrupt INT0[4] Signal                                        |

| 10               | 21                      | AIN[4]          |     | Can be used as an interrupt input or as an analog signal input. |

| 18               | 23                      | INT0[5]         |     | Interrupt INT0[5] Signal                                        |

| 10               | 25                      | AIN[5]          |     | Can be used as an interrupt input or as an analog signal input. |

| 20               | 25                      | INT0[6]         |     | Interrupt INT0[6] Signal                                        |

| 20               | 20                      | AIN[6]          | I   | Can be used as an interrupt input or as an analog signal input. |

| 22               | 27                      | INT0[7]         | I   | Interrupt INT0[7] Signal                                        |

| 22               | 21                      | AIN[7]          |     | Can be used as an interrupt input or as an analog signal input. |

|                  |                         |                 |     | Interrupt INT2[0] Signal                                        |

| 36               | 42                      | INT2[0]<br>TXD0 | I   | Can be used as an interrupt input.                              |

|                  |                         | 1712 0          |     | This pin shares with pin TXD0.                                  |

|                  |                         |                 |     | Interrupt INT2[1] Signal                                        |

| 37               | 37 43                   | INT2[1]<br>RXD0 | 10  | Can be used as an interrupt input.                              |

|                  |                         |                 |     | This pin shares with pin RXD0.                                  |

|                  |                         | INT2[2]         |     | Interrupt INT2[2] Signal                                        |

| 38               | 44                      | TXD1            | I   | Can be used as an interrupt input.                              |

|                  |                         |                 |     | This pin shares with pin TXD1.                                  |

| <b>Pin #</b><br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name          | I/O | Description                                                                                                                                                                                                                                                               |

|-------------------------|-------------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | 9 45                    | INT2[3]<br>RXD1   |     | Interrupt INT2[3] Signal                                                                                                                                                                                                                                                  |

| 39                      |                         |                   | Ю   | Can be used as an interrupt input.                                                                                                                                                                                                                                        |

|                         |                         |                   |     | This pin shares with pin RXD1.                                                                                                                                                                                                                                            |

|                         |                         | INT2[4]           |     | Interrupt INT2[4] Signal                                                                                                                                                                                                                                                  |

| 92                      | 127                     | TXD2              | I   | Can be used as an interrupt input.                                                                                                                                                                                                                                        |

|                         |                         |                   |     | This pin shares with pin TXD2.                                                                                                                                                                                                                                            |

|                         |                         | INT2[5]           |     | Interrupt INT2[5] Signal                                                                                                                                                                                                                                                  |

| 4                       | 7                       | RXD2              | 10  | Can be used as an interrupt input.                                                                                                                                                                                                                                        |

|                         |                         |                   |     | This pin shares with pin RXD2.                                                                                                                                                                                                                                            |

|                         |                         | INT2[6]           |     | Interrupt INT2[6] Signal                                                                                                                                                                                                                                                  |

| 40                      | 46                      | CANTX             | I   | Can be used as an interrupt input.                                                                                                                                                                                                                                        |

|                         |                         | OANTA             |     | This pin shares with pin CANTX.                                                                                                                                                                                                                                           |

|                         |                         | INT2[7]           |     | Interrupt INT2[7] Signal                                                                                                                                                                                                                                                  |

| 41                      | 47                      | CANRX             | 10  | Can be used as an interrupt input.                                                                                                                                                                                                                                        |

|                         |                         | 0, 111 0.         |     | This pin shares with pin CANRX.                                                                                                                                                                                                                                           |

|                         |                         | INT1[0]           |     | Interrupt INT1[0] Signal                                                                                                                                                                                                                                                  |

| 35                      | 41                      | CLKOUT            | 10  | Can be used as an interrupt input.                                                                                                                                                                                                                                        |

|                         |                         |                   |     | This pin shares with pin CLKOUT.                                                                                                                                                                                                                                          |

| 14                      | 19                      | INT1[3]           | 10  | Interrupt INT1[3] Signal                                                                                                                                                                                                                                                  |

|                         | 10                      |                   |     | Can be used as an interrupt input.                                                                                                                                                                                                                                        |

|                         |                         |                   |     | Interrupt INT1[6] Signal                                                                                                                                                                                                                                                  |

| 34                      | 40                      | INT1[6]<br>RSTOUT | 10  | Can be used as an interrupt input.                                                                                                                                                                                                                                        |

|                         |                         | RSTOUT            |     | This pin shares with pin RSTOUT.                                                                                                                                                                                                                                          |

| 42                      | 48                      |                   |     | Interrupt INT1[7] Signal                                                                                                                                                                                                                                                  |

| 42                      | 40                      | INT1[7]           | 10  | Can be used as an interrupt input.                                                                                                                                                                                                                                        |

|                         |                         |                   |     | LCD Interrupt Output Signal                                                                                                                                                                                                                                               |

|                         | 55                      | LCD_INT#          | 0   | When the interrupt condition set by the LCD controller occurs,                                                                                                                                                                                                            |

|                         | 00                      |                   | Ŭ   | this pin becomes low and is used to generate an interrupt                                                                                                                                                                                                                 |

|                         |                         |                   |     | output to inform the MCU.                                                                                                                                                                                                                                                 |

|                         |                         |                   |     | GPIO Output/Input Signals of LCD Controller                                                                                                                                                                                                                               |

| , 50,                   | 83, 62,                 | GPIOC[7]          |     | These signals are controlled by the register of the LCD controller inside LT7589, and the output data of GPOC[7] shares nine with LCD_PW/M/01                                                                                                                             |

| 49, 45,<br>44, 48,      | 61, 57,<br>56, 60,      |                   | ю   | shares pins with LCD_PWM[0].                                                                                                                                                                                                                                              |

| 47, 46, 47, 46          | 59, 58                  | GPIUC[6:0]        |     | GPOC [6:0] shares pins with {XSIO3, XSIO2, SFC[1] #, SFC[0]<br>#, XSIO1, XSIO0, SFCLK} and can only be used when the<br>functions of LCD_PWM and SPI Master are disabled. The<br>output mode of these pins can be set through the registers of<br>the TFT LCD controller. |

| Pin #<br>LT7589A                                 | <b>Pin #</b><br>LT7589B                               | Pin Name     | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------|-------------------------------------------------------|--------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80,<br>63,<br>79,<br>78,<br>70,<br>69,<br>62, 61 | 112,<br>94,<br>111,<br>100,<br>101,<br>100,<br>93, 92 | GPIOD[7:0]   | 10  | GPIO Output/Input Signals of LCD Controller<br>These signals are controlled by the register of the LCD<br>controller inside LT7589, and the output data of GPOD [7:0]<br>shares pins with {PD[18], PD[2], PD[17], PD[16], PD[9], PD[8],<br>PD[1], PD[0]}.<br>GPOD[7:0] can only be used when the LCD panel data bus is<br>set to 16 bits. The output mode of these pins can be set through<br>the registers of the TFT LCD controller. |

|                                                  | 54~49                                                 | LCD_IOA[7:2] | Ю   | <b>GPIO Output/Input Signals of LCD Controller</b><br>The output/input modes of these pins can be set through the registers of the TFT LCD controller.                                                                                                                                                                                                                                                                                 |

### 6.8 ADC Input Signals

| Pin #<br>LT7589A                        | Pin #<br>LT7589B                        | Pin Name                     | I/O | Description                                                                                                                                                                   |

|-----------------------------------------|-----------------------------------------|------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22, 20,<br>18, 16,<br>21, 19,<br>17, 15 | 27, 25,<br>23, 21,<br>26, 24,<br>22, 20 | <b>AIN[7:0]</b><br>INT0[7:0] | Ю   | Analog Input Signals<br>These analog signals are used as ADC analog input channels.<br>When not configured as analog inputs, these signals can also<br>be used for INT0[7:0]. |

#### Table 6-8: ADC Input Signals

### 6.9 Miscellaneous Signals

#### Table 6-9: Miscellaneous Signals

| Pin #<br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name      | I/O | Description                                                                                                                                                                                     |

|------------------|-------------------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                         |               |     | Waiting for Output Signal                                                                                                                                                                       |

| 43               | 77                      | LCD_WAIT#     | 0   | When the internal MCU performs read and write control on the LCD control circuit, if it is in a busy state, WAIT # will be set to a low potential to inform the MCU to enter the waiting cycle. |

|                  |                         |               |     | LCD Control Circuit Chip Selection Signal                                                                                                                                                       |

|                  | 125                     | LCD_CS#<br>NC | I   | LCD_CS# = 0, Represents the command or data read/write cycle of the internal MCU to the LCD control circuit.                                                                                    |

|                  |                         |               |     | Note: This pin has already been internally connected to the EBI-CS # of the MCU and must be kept in NC.                                                                                         |

|                  |                         |               |     | Reset Input Signal for LCD Control Circuit                                                                                                                                                      |

| 91               | 124                     | LCD_RST#      | I   | When RST #=0 and maintains a length greater than 32 clock cycles, LT7586 will generate a reset action.                                                                                          |

|                  |                         |               |     | I2C Clock Signal                                                                                                                                                                                |

|                  | 126                     | SCL           | 10  | This signal is used as the clock signal for I2C of MCU or GPIO.                                                                                                                                 |

|                  |                         |               |     | Note: This pin should be connected to the LCD_RST # of Pin-<br>124 to control whether the LCD circuit performs a reset action.                                                                  |

| <b>Pin #</b><br>LT7589A | <b>Pin #</b><br>LT7589B | Pin Name               | I/O | Description                                                                            |

|-------------------------|-------------------------|------------------------|-----|----------------------------------------------------------------------------------------|

|                         |                         |                        |     | Flash Programming Clock Signal                                                         |

| 4                       |                         | SWDCK<br>RXD2, INT2[5] | Ι   | This input signal is the clock signal used for programming internal flash memory.      |

|                         |                         | 1002, 1012[0]          |     | This pin is also connected to RXD2 and INT2[5], it's a shared pin.                     |

|                         |                         |                        |     | Flash Programming Data Signal                                                          |

| 92                      | 127                     | SWDIO                  | Ι   | This input signal is used as a data signal for programming internal flash memory.      |

|                         |                         | TXD2, INT2[4]          |     | This pin is also connected to TXD2 and INT2[4], it's a shared pin.                     |

|                         |                         | CLKOUT<br>INT1[0]      | 0   | System Clock Signal Output                                                             |

| 35                      | 41                      |                        |     | This output signal reflects the internal system clock.                                 |

|                         |                         |                        |     | When not configured as a clock output, this signal can also be used for INT1[0].       |

|                         |                         |                        |     | MCU Reset Output Signal                                                                |

|                         |                         | RSTOUT                 |     | This output signal indicates that the internal reset controller is resetting the chip. |

| 34                      | 40                      |                        | 0   | 0 = The chip is in a reset state                                                       |

|                         |                         | INT1[6]                |     | 1 = chip not reset state                                                               |

|                         |                         |                        |     | When not configured as a reset output, this signal can also be used for INT1[6].       |

|                         |                         |                        |     | MCU Reset Input Signal                                                                 |

| 33                      | 39                      | RESET#                 |     | When RESET #=0, a reset action will be performed on the internal MCU.                  |

### 6.10 Power and Clock Signals

Table 6-10: Power and Clock Signals