## High Performance 32bit Micro Controller

### Introduction

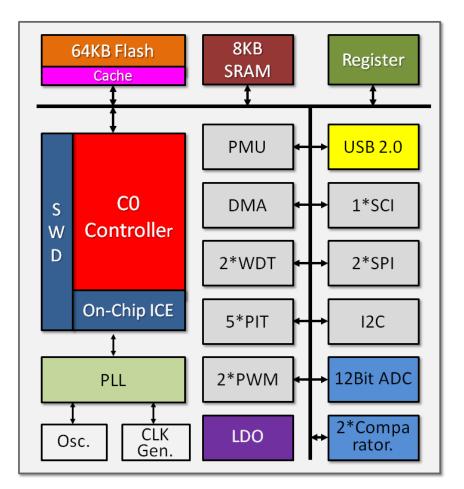

The LT32x02 incorporates the High-performance C0 32-bit RISC core operating at a 72MHz maximum frequency with high-speed embedded Flash memories (Flash up to 64Kbytes which contains an 1kbytes two-way set associative read Cache and SRAM up to 8Kbytes), and an extensive range of enhanced peripherals and I/Os. All devices offer standard communication interfaces, including two Master SPI, one I2C, one UART. The LT32U02 also provide one USB2.0 Fast Speed controller. Both of LT3202 support up to four General-purpose 16-bit timers, one embedded programmable 24-bit timers, eight advanced-control PWM timers and two asynchronous Watch Dog Timers. It also provides Analog modules including one 1MSPS ADC with 8-channels and two Comparators.

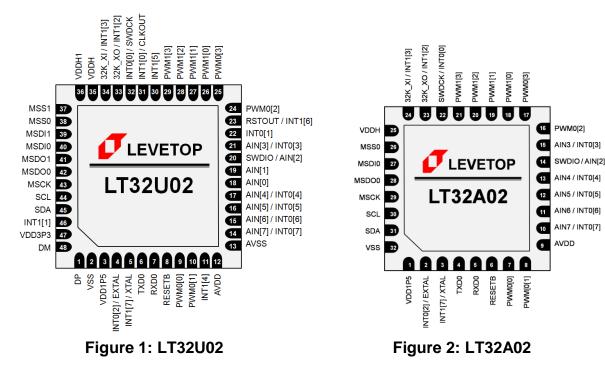

The LT32U02 is QFN-48pin package, LT32A02 is QFN-32pin package. The operation temperature range is -40°C to 85°C and the operating voltage is 2.0/2.8~5.5V.

# Pin Assignment

# **Features**

#### **C0** Processor

- \_ 32-bit Load/Store Reduced Instruction set Computer (RISC) Architecture with fixed 16-bit Instruction Length

- \_ 16 Entry 32-bit General-Purpose Register File

- \_ Efficient 3-Stage Execution Pipeline, Hidden from Application Software

- \_ Single-cycle Instruction Execution for many Instructions, Three Cycles for Branches

- \_ Support for Byte / Half-word / Word Memory Accesses

- \_ Embedded Interrupt Controller, support Nested Vector Interrupts.

- \_ Single-cycle 32-bit x 32-bit Hardware Integer Multiplier Array

- \_ 3~13 Cycles Hardware Integer Divider Array

### 8K Bytes of Static Random-Access Memory (SRAM)

\_ Single Cycle Byte, Half-word (16-bit), and Word (32-bit) Reads and Writes

### ■ 64K Bytes Embedded Flash (EFLASH)

- \_ Page Erase Capability: 512 bytes per Page

- \_ Read Cycle Time: 40ns (min)

- \_ Endurance: 100000 Cycles (min)

- Greater than 20 Years Data Retention

- \_ Fast Page Erase/ Byte Program

- Half-word Program Time: 7.5us (max)

- Page Erase Time: 5 ms (max)

- Mass Erase Time: 40 ms (max)

- \_ Single Cycle Byte, Half-word (16-bit) and Word (32-bit) Read Access.

#### Reset

\_ Internal power on reset circuit

- \_ Five sources of reset:

- Power-on Reset

- External Pin

- Software Reset

- Watchdog Timer

- Program Voltage Detect Reset

- \_ Status Flag Indicates Source of Last Reset

#### Four Periodic Interval Timer

- \_ 16-bit Counter with Modulus "initial count" Register

- \_ Selectable as Free Running or Count down

- \_ 16 Selectable Prescalars  $\rightarrow$  2<sup>0</sup> to 2<sup>15</sup>

#### Two Watchdog Timer

- \_ 16-bit Counter with Modulus "Initial Count" Register

- \_ Pause Option for Low-power Modes

- \_ Up to 2000ms Service Time

#### Two External Interrupts Port (EPORT)

- \_ Eight Channels for Each EPORT

- \_ Rising/falling Edge Select

- \_ Low/High-Level Sensitive

- \_ Interrupt Pins Configurable as General-purpose I/O

#### Two Serial Peripheral Interface Master Module (SPI)

- \_ SPI Master Mode

- \_ Shared SPICLK Ports

- \_ Two 4 Entries deep Read FIFO

- \_ Two 4 Entries deep Write FIFO

- \_ Interrupt Generation after 1, 2, 3, or 4 Transferred Bytes

- \_MSB/LSB Selectable

- \_ Variable Baud-rate During Communication

- \_ Serial Clock with Programmable Polarity and Phase

- \_ 16/32 bit Transmit/Receive Data Width

- \_ Byte Re-order

- \_ Controllable Slave Select (spiss0/1) bit

#### One Serial Communications Interface Module (SCI)

- \_ Standard Mark/Space Non-Return-to-Zero (NRZ) format

- \_ The Baud Rate Divisor is a 22-bit Number Consisting of 16-bit Integer and 6-bit Fractional Part

- \_ Programmable 7-bit, 8-bit or 9-bit Data Format

- \_ Separately enabled Transmitter and Receiver

- \_ Separate Receiver and Transmitter Central Processor unit (CPU) Interrupt Requests

- \_ Programmable Transmitter Output Polarity

- \_ Two Receiver Wakeup Methods:

- Idle Line Wakeup

- Address Mark Wakeup

- \_ Interrupt-driven Operation with Eight Flags:

- Transmitter Empty

- Transmission Complete

- Receiver Full

- Idle receiver Input

- Receiver Overrun

- Noise Error

- Framing Error

- Parity Error

- \_ Receiver Framing Error Detection

- \_ Hardware Parity Checking

- \_ 1/16 bit-time Noise Detection

- \_ General-purpose, I/O Capability

- \_ Serial IR Interface Low-speed, IrDA-Compatible (up to 115.2Kbit/s)

#### One USB2.0 Full Speed Compatible Device (LT32U02 Only)

- \_ Supports Internal Reference Clock or External 12MHz Crystal Reference Clock

- \_ Compliant with USB2.0 Full Speed Specification with on-chip Integrated PHY Module

- \_ Supports FS (12Mbps) Mode

- \_ Up to 8 Endpoints Supported Including Endpoint 0

- \_ All Endpoints except Endpoint 0 can support Interrupt and Bulk Transfer

- \_ All Endpoints except Endpoint 0 can be Configured as 8, 16, 32, 64 bytes FIFO size

- \_ Endpoint 0 Support Control Transfer

#### Two Pulse Width Modulator (PWM)

- \_ Four Channel each PWM Controller

- \_ Programmable Period

- \_ Programmable Duty Cycle

- \_ Two Dead-Zone Generator

- \_ Capture Function

- \_ Pins can be Configured as General-purpose I/O

#### ■ ADC with 8-Channel

- \_ High Performance

- 12-bit, 10-bit, 8-bit or 6-bit configurable resolution

- ADC Conversion Time: 1.0µs for 12-bit Resolution (1 MHz), 0.88µs Conversion Time for 10 bit Resolution, Faster Conversion times can be obtained by Lowering Resolution.

- Programmable Sampling Time

- Data Alignment with Built-in Data Coherency

- DMA Support

- \_ Low Power

- Application cans Reduce PLCK Frequency for Low Power Operation while still Keeping Optimum ADC Performance. For Example, 1.0µs Conversion Time is kept, whatever the Frequency of PCLK.

- Wait mode: Prevents ADC Overrun in Applications with Low Frequency PLCK

- Auto off mode: ADC is Automatically Powered Off Except during the Active Conversion phase. This Dramatically Reduces the Power Consumption of the ADC.

- \_ Analog Input Channels

- 8 External Analog Inputs

- 1 Channel for Internal Reference Voltage

- 1 Channel for Internal Temperature Sensor

- \_ Start-of-Conversion can be Initiated:

- By Software

- By Hardware Triggers with Configurable Polarity

- \_ Conversion Modes

- Can Convert a Single Channel or can Scan a Sequence of Channels.

- Single Mode Converts Selected Inputs once per Trigger

- Continuous Mode Converts Selected Inputs Continuously

- Discontinuous Mode

- \_ Interrupt Generation at the end of Sampling, end of Conversion, end of Sequence Conversion, and in case of Analog Watchdog or Overrun Events.

- \_ Analog Watchdog

- Single-ended and Differential-input Configurations

- Converter uses an Internal Reference or an External Reference

#### **Two Analog Comparators**

- \_ Programmable Response Time

- \_ Programmable Hysteresis

- \_ Support Analog input Multiplexer with Nine Selection

- \_ Two Optional Outputs: Filtered or Asynchronous Output

- \_ Selectable Rising/Falling Edge Interrupt

#### PMU

- \_ Support 3.3V LDO (for USB PHY Power Supply) with Maximum Load Current 100mA

- \_ 3.3V LDO Support Power Down for Save Power Consumption

- \_ Support 1.5V LDO with Maximum Load Current 50mA

- \_ 1.5V LDO Support Four Mode: Normal, Lower power, High power

#### Programmable Voltage Detector

#### Internal Oscillator

- \_ 128KHz Oscillator Clock for Watchdog and PMU

- \_72MHz Oscillator Clock which can be used for System Clock

- \_ 48MHz USBPLL Clock which can be used for System Clock

#### **External Crystal Oscillator**

\_ Up to 20Mhz External Crystal Oscillator Clock which can be used for System Clock \_ 32.768Khz External Crystal Oscillator Clock which can be used for Watchdog

## Block Diagram

Figure 3: Block Diagram

## Signal Properties Summary

| Name            | Alternate       | Qty. | Dir.   | Input Sync | Pullup <sup>1</sup> | Output Drive            |  |  |

|-----------------|-----------------|------|--------|------------|---------------------|-------------------------|--|--|

| SCI (2)         |                 |      |        |            | •                   | (ST/OD/SP) <sup>2</sup> |  |  |

| SCI (2)<br>RXD0 |                 | 1    | I/O    | N          | Dullup              | ST                      |  |  |

| TXD0            |                 | 1    | 1/O    | N          | Pull-up             | ST                      |  |  |

|                 |                 |      | 1/0    | IN         | Pull-up             | 51                      |  |  |

| USB (2)<br>DP   |                 | 4    | Anolog |            |                     | SP                      |  |  |

|                 |                 | 1    | Analog |            |                     |                         |  |  |

| DM              |                 | 1    | Analog |            |                     | SP                      |  |  |

|                 |                 |      | 1/0    | NI         | Dulling             | 00                      |  |  |

| SCL             |                 | 1    | I/O    | N          | Pull-up             | OD                      |  |  |

| SDA             |                 | 1    | I/O    | Ν          | Pull-up             | OD                      |  |  |

| SPI (7)         |                 | 4    | 1/0    | K I        |                     | 0 <b>T</b>              |  |  |

| MSS0            |                 | 1    | I/O    | N          | -                   | ST                      |  |  |

| MSDI0           |                 | 1    | I/O    | N          | Pull-up             | ST                      |  |  |

| MSDO0           |                 | 1    | I/O    | N          | -                   | ST                      |  |  |

| MSS1            |                 | 1    | I/O    | N          | -                   | ST                      |  |  |

| MSDI1           |                 | 1    | I/O    | N          | Pull-up             | ST                      |  |  |

| MSDO1           |                 | 1    | I/O    | N          | -                   | ST                      |  |  |

| MSCK            |                 | 1    | I/O    | N          | -                   | ST                      |  |  |

| PWM0 (4)        |                 | T    |        |            |                     |                         |  |  |

| PWM0[0]         |                 | 1    | I/O    | N          | Pull-up             | ST                      |  |  |

| PWM0[1]         |                 | 1    | I/O    | N          | Pull-up             | ST                      |  |  |

| PWM0[2]         |                 | 1    | I/O    | Ν          | Pull-up             | ST                      |  |  |

| PWM0[3]         |                 | 1    | I/O    | Ν          | Pull-up             | ST                      |  |  |

| PWM1 (2)        |                 | -    |        |            |                     |                         |  |  |

| PWM1[0]         |                 | 1    | I/O    | N          | Pull-up             | ST                      |  |  |

| PWM1[1]         |                 | 1    | I/O    | N          | Pull-up             | ST                      |  |  |

| PWM1[2]         |                 | 1    | I/O    | Ν          | Pull-up             | ST                      |  |  |

| PWM1[3]         |                 | 1    | I/O    | Ν          | Pull-up             | ST                      |  |  |

| ADC (7)         |                 |      |        |            |                     |                         |  |  |

| AIN[7:3]        | INT0[7:3]       | 5    | Mixed  | Ν          | -                   | -                       |  |  |

| AIN[1:0]        | -               | 2    | Analog | Ν          | -                   | -                       |  |  |

| Edge Port 1     | Edge Port 1 (5) |      |        |            |                     |                         |  |  |

| INT1[1]         |                 | 1    | I/O    | Ν          | Pull-up             | ST                      |  |  |

| INT1[2]         | 32K_XO          | 1    | I/O    | Ν          | Pull-up             | ST                      |  |  |

| INT1[3]         | 32K_XI          | 1    | I/O    | Ν          | Pull-up             | ST                      |  |  |

| INT1[4]         |                 | 1    | I/O    | Ν          | Pull-up             | ST                      |  |  |

| INT1[5]         |                 | 1    | I/O    | Ν          | Pull-up             | ST                      |  |  |

**Table 1: Signal Properties Summary**

| Name            | Alternate | Qty. | Dir. | Input Sync | Pullup <sup>1</sup> | Output Drive<br>(ST/OD/SP) <sup>2</sup> |  |

|-----------------|-----------|------|------|------------|---------------------|-----------------------------------------|--|

| Edge Port 0 (1) |           |      |      |            |                     |                                         |  |

| INT0[1]         | -         | 1    | I/O  | N          | Pull-up             | ST                                      |  |

| Debug Port      | (2)       |      |      |            |                     |                                         |  |

| SWDIO           | AIN[2]    | 1    | I/O  | N          | Pull-up             | ST                                      |  |

| SWDCK           | INT0[0]   | 1    | I/O  | N          | Pull-up             | ST                                      |  |

| Clock (3)       |           |      |      |            |                     |                                         |  |

| EXTAL           | INT0[2]   | 1    | I/O  | N          | -                   | SP                                      |  |

| XTAL            | INT1[7]   | 1    | I/O  | N          | -                   | SP                                      |  |

| CLKOUT          | INT1[0]   | 1    | I/O  | N          | Pull-up             | ST                                      |  |

| RESET (2)       |           |      |      |            |                     |                                         |  |

| RESETB          | -         | 1    | -    | Y          | -                   | SP                                      |  |

| RSTOUT          | INT1[6]   | 1    | I/O  | N          | Pull-up             | ST                                      |  |

| Power Sup       | ply       |      |      |            |                     |                                         |  |

| VDDH            | -         | -    | -    | -          | -                   | SP                                      |  |

| VDDH1           | -         | -    | -    | -          | -                   | SP                                      |  |

| VDD3P3          | -         | -    | -    | -          | -                   | SP                                      |  |

| VDD1P5          | -         | -    | -    | -          | -                   | SP                                      |  |

| VSS             | -         | -    | -    | -          | -                   | SP                                      |  |

| AVDD            | -         | -    | -    | -          | -                   | SP                                      |  |

| AVSS            | -         | -    | -    | -          | -                   | SP                                      |  |

#### Table 1: Signal Properties Summary (Continued)

#### Notes:

- 1. All Pull-ups are disconnected when the signal is programmed as an output.

- 2. Output Driver Type: ST=Standard, SP=Special, OD=Standard Driver with Open-Drain Pull down option selected.

### Signal Descriptions

| Pin Name  | Pin Number |         | Pin Description                                                                                                                                                                                                                             |

|-----------|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fill Name | LT32U02    | LT32A02 |                                                                                                                                                                                                                                             |

| RXD0      | 7          | 5       | <b>Receive Data</b><br>This is a Serial Communications Interface 0<br>Module Signal (SCI0). This signal is used for the<br>SCI receiver data input and is also available for<br>GPIO when not configured for receiver<br>operation.         |

| TXD0      | 6          | 4       | <b>Transmit Data</b><br>This is a Serial Communications Interface 0<br>Module Signal (SCI0). This signal is used for the<br>SCI transmitter data output and is also available<br>for GPIO when not configured for transmitter<br>operation. |

| DP        | 1          |         | <b>USB Data Positive</b><br>These signals are used by the USB module.                                                                                                                                                                       |

| DM        | 48         |         | <b>USB Data Negative</b><br>These signals are used by the USB module.                                                                                                                                                                       |

| SCL       | 44         | 30      | <b>I2C Clock</b><br>This signal is used for the I2C clock line signal<br>and is also available for GPIO when not<br>configured for receiver operation.                                                                                      |

| SDA       | 45         | 31      | <b>I2C Data</b><br>This signal is used for the I2C data line signal<br>and is also available for GPIO when not<br>configured for transmitter operation.                                                                                     |

| MSDO0     | 42         | 28      | Master 0 Out<br>This signal is the serial data output from the SPI0<br>in master mode.                                                                                                                                                      |

| MSDO1     | 41         |         | <b>Master 1 Out</b><br>This signal is the serial data output from the SPI1<br>in master mode.                                                                                                                                               |

| MSDIO     | 40         | 27      | Master 0 In<br>This signal is the serial data input to the SPI0 in<br>master mode.                                                                                                                                                          |

| MSDI1     | 39         |         | Master 1 In<br>This signal is the serial data input to the SPI1 in<br>master mode.                                                                                                                                                          |

### **Table 2: Signal Descriptions**

|           | Pin N       | umber       | Din Description                                                                                                                                                                |  |  |  |  |

|-----------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| n Name    | LT32U02     | LT32A02     | Pin Description                                                                                                                                                                |  |  |  |  |

| MSCK      | 43          | 29          | Master Serial Clock<br>The serial clock synchronizes data transmissions<br>between master and slave devices. MSCK is an<br>output and is shared between with SPI0 and<br>SPI1. |  |  |  |  |

| MSSO      | 38          | 26          | <b>Slave Select 0</b><br>This output signal is the peripheral chip select signal in master mode.                                                                               |  |  |  |  |

| MSS1      | 37          |             | <b>Slave Select 1</b><br>This output signal is the peripheral chip select<br>signal in master mode                                                                             |  |  |  |  |

| INT0[7]   | 14          | 10          |                                                                                                                                                                                |  |  |  |  |

| INT0[6]   | 15          | 11          |                                                                                                                                                                                |  |  |  |  |

| INT0[5]   | 16          | 12          |                                                                                                                                                                                |  |  |  |  |

| INT0[4]   | 17          | 13          | <b>Edge Port 0 Signals</b><br>These bidirectional signals function as either<br>external interrupt sources or GPIO.                                                            |  |  |  |  |

| INT0[3]   | 21          | 15          |                                                                                                                                                                                |  |  |  |  |

| INT0[2]   | 4           | 2           |                                                                                                                                                                                |  |  |  |  |

| INT0[1]   | 22          |             |                                                                                                                                                                                |  |  |  |  |

| INT0[0]   | 32          | 22          |                                                                                                                                                                                |  |  |  |  |

| INT1[7]   | 5           | 3           |                                                                                                                                                                                |  |  |  |  |

| INT1[6]   | 23          |             |                                                                                                                                                                                |  |  |  |  |

| INT1[5]   | 30          |             |                                                                                                                                                                                |  |  |  |  |

| INT1[4]   | 11          |             | Edge Port 1 Signals                                                                                                                                                            |  |  |  |  |

| INT1[3]   | 34          |             | These bidirectional signals function as either external interrupt sources or GPIO.                                                                                             |  |  |  |  |

| INT1[2]   | 33          |             |                                                                                                                                                                                |  |  |  |  |

| INT1[1]   | 46          |             |                                                                                                                                                                                |  |  |  |  |

| INT1[0]   | 31          |             |                                                                                                                                                                                |  |  |  |  |

| PWM0[3:0] | 25,24,10,9  | 17,16,8,7   | <b>Pulse Width Modulator 0 Signals</b><br>These out signals function as either PMW0<br>output or GPIO.                                                                         |  |  |  |  |

| PWM1[3:0] | 29,28,27,26 | 21,20,19,18 | <b>Pulse Width Modulator 1 Signals</b><br>These out signals function as either PMW1<br>output or GPIO.                                                                         |  |  |  |  |

### Table 2: Signal Descriptions (Continued)

|          | Pin Number |         | Din Description                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|----------|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name | LT32U02    | LT32A02 | Pin Description                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| AIN[7]   | 14         | 10      |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| AIN[6]   | 15         | 11      |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| AIN[5]   | 16         | 12      |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| AIN[4]   | 17         | 13      | Analog-to-Digital Converter Signals                                                                                                                                                                                                                                                                              |  |  |  |  |

| AIN[3]   | 21         | 15      | These analog signals function as ADC analog channels.                                                                                                                                                                                                                                                            |  |  |  |  |

| AIN[2]   | 20         | 14      |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| AIN[1]   | 19         |         |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| AIN[0]   | 18         |         |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| SWDCLK   | 32         | 22      | <b>Test Clock</b><br>This input signal is the test clock used to<br>synchronize the SWD logic.                                                                                                                                                                                                                   |  |  |  |  |

| SWDIO    | 20         | 14      | <b>Test Data Input / Output</b><br>This input/output signal is the serial input/output<br>for test instructions and data.                                                                                                                                                                                        |  |  |  |  |

| EXTAL    | 4          | 2       | Fast Oscillator Pad Input<br>The signal is the input of fast Oscillator Pad.                                                                                                                                                                                                                                     |  |  |  |  |

| XTAL     | 5          | 3       | Fast Oscillator Pad output<br>The signal is the output fast Oscillator pad.                                                                                                                                                                                                                                      |  |  |  |  |

| 32K_XI   | 34         | 24      | <b>32.768Khz Oscillator Pad input</b><br>The signal is the input of 32.768Khz Oscillator<br>Pad.                                                                                                                                                                                                                 |  |  |  |  |

| 32K_XO   | 33         | 23      | <b>32.768Khz Oscillator Pad output</b><br>The signal is the output 32.768Khz Oscillator<br>pad.                                                                                                                                                                                                                  |  |  |  |  |

| CLKOUT   | 31         |         | <b>Clock Out</b><br>This output signal reflects the internal system clock.                                                                                                                                                                                                                                       |  |  |  |  |

| RESETB   | 8          | 6       | <ul> <li>Reset In</li> <li>This active-low input signal is used as the external reset request. Reset places the CPU in supervisor mode with default settings for all register bits except some register bits only reset by POR.</li> <li>0 = external reset assert</li> <li>1 = external reset desert</li> </ul> |  |  |  |  |

### Table 2: Signal Descriptions (Continued)

| Pin Name | Pin Number |         | Pin Description                                                                                                                                                                                                         |  |  |

|----------|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Fin Name | LT32U02    | LT32A02 | Pill Description                                                                                                                                                                                                        |  |  |

| RSTOUT   | 23         |         | <ul> <li>Reset Out</li> <li>This active-low output signal is an indication that the internal reset controller has reset the chip.</li> <li>0 = chip is at reset status</li> <li>1 = chip is not reset status</li> </ul> |  |  |

| VDDH     | 35         | 25      | <b>Power</b><br>This signal supplies 2.5~5.5V positive power to<br>the I/O pads and LDO.                                                                                                                                |  |  |

| VDDH1    | 36         |         | <b>Power</b><br>This signal supplies 2.5~5.5V positive power to<br>the SPI I/O pads. VDDH1 is short together with<br>VDDH in QFN32 package.                                                                             |  |  |

| VDD3P3   | 47         |         | <b>Power</b><br>3.3V LDO output signal and is used to supply the<br>power of USB transceiver. 1uF ceramic bypass<br>capacitor is required to externally connect<br>between the pad and vss.                             |  |  |

| VDD1P5   | 3          | 1       | <b>Core Power</b><br>1.5V LDO output signal and is used to supply the<br>power of the core logic. 1uF ceramic bypass<br>capacitor is required to externally connect<br>between the pad and vss.                         |  |  |

| VSS      | 2          | 32      | <b>Ground</b><br>This signal supplies 2.5~5.5V negative supply<br>(ground) to the I/O pads and LDO.                                                                                                                     |  |  |

| AVDD     | 12         | 9       | <b>Analog Power</b><br>This signal supplies 2.5~5.5V positive power to<br>analog module.                                                                                                                                |  |  |

| AVSS     | 13         |         | <b>Analog Ground</b><br>This signal is the negative supply to the Analog<br>module.                                                                                                                                     |  |  |

#### Table 2: Signal Descriptions (Continued)

#### Notes:

- 1. The SPI signals are used by the SPI modules and may also be configured to be discrete I/O signals.

- 2. The VDD and VSS signals provide system power and ground to the chip. Multiple signals are provided for adequate current capability. All power supply signals must have adequate bypass capacitance for high-frequency noise suppression.

## Absolute Maximum Ratings

Maximum ratings are the extreme limits to which the MCU can be exposed without permanently damaging it. See Table 3. The MCU contains circuitry to protect the inputs against damage from high static voltages; however, do not apply voltages higher than those shown in the table. Connect unused inputs to the appropriate voltage level, either  $V_{SSH}$  or  $V_{DDH}$ . This device is not guaranteed to operate properly at the maximum ratings. Refer to "DC Electrical Specifications" for guaranteed operating conditions.

| Num | Rating                      | Symbol     | Value        | Unit |

|-----|-----------------------------|------------|--------------|------|

| 1   | Supply Voltage              | $V_{ddh}$  | -0.5 to +5.5 | V    |

| 2   | Supply Voltage              | $V_{ddh1}$ | -0.5 to +5.5 | V    |

| 3   | Input Voltage <sup>1</sup>  | Avdd       | -0.5 to +5.5 | V    |

| 4   | Operating Temperature Range | TOPT       | -40 to +85   | °C   |

#### Table 3: Absolute Maximum Ratings

## DC Electrical Specifications

#### **Table 4: DC Electrical Specifications**

| Parameter                                                            | Symbol          | Min                                  | Typical | Мах               | Unit |

|----------------------------------------------------------------------|-----------------|--------------------------------------|---------|-------------------|------|

| Supply Voltage                                                       | $V_{ddh}$       | 2.0<br>(LT32A02)<br>2.8<br>(LT32U02) | 3.3/5.0 | 5.5               | V    |

| Input High Voltage                                                   | V <sub>IH</sub> | $0.65^{*}V_{ddh}$                    | -       | $V_{ddh}$         | V    |

| Input Low Voltage                                                    | V <sub>IL</sub> | $V_{SS}$                             | -       | $0.35^{*}V_{ddh}$ | V    |

| Output High Voltage                                                  | V <sub>OH</sub> | 0.8*V <sub>ddh</sub>                 | _       | _                 | V    |

| Output Low Voltage                                                   | V <sub>OL</sub> | —                                    | _       | $0.1^{*}V_{ddh}$  | V    |

| Pull-Up Resistor                                                     | R <sub>PU</sub> | 20                                   |         | 100               | Kohm |

| Pull-Down Resistor                                                   | R <sub>PU</sub> | 20                                   |         | 100               | Kohm |

| Low Level Output Current @<br>V <sub>OL</sub> =0.1*V <sub>ddh</sub>  | I <sub>OL</sub> |                                      |         | 6                 | mA   |

| High Level Output Current @<br>V <sub>OH</sub> =0.8*V <sub>ddh</sub> | I <sub>OH</sub> |                                      |         | 6                 | mA   |